Zen 5は、AMDにとってZen 2以来の大きなアーキテクチャー刷新となる。

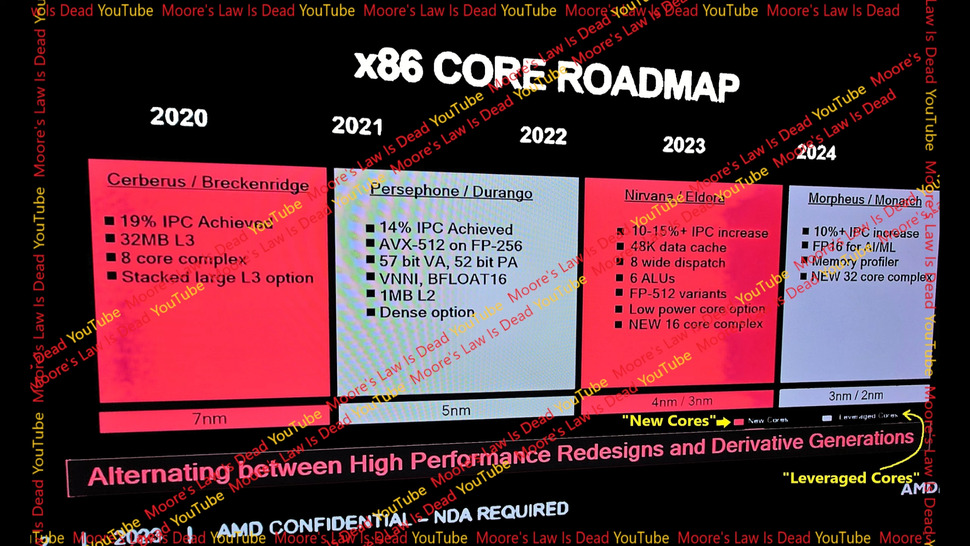

YouTubeチャンネル「Moore's Law Is Dead」が、Zen 5とZen 6の主要仕様とIPC目標を詳述したAMD公式とされる2枚の新しいスライドをリークした。

この新しいスライドによると、Zen 5はZen 4からアーキテクチャを大幅に見直し、10~15%以上のIPC向上を目指すという。

また、Zen 5では初めて16コアのCCXが搭載されると報じられている。

これ以上先に進む前に、このレポートに健全な量の塩を振りかける必要があるだろう。

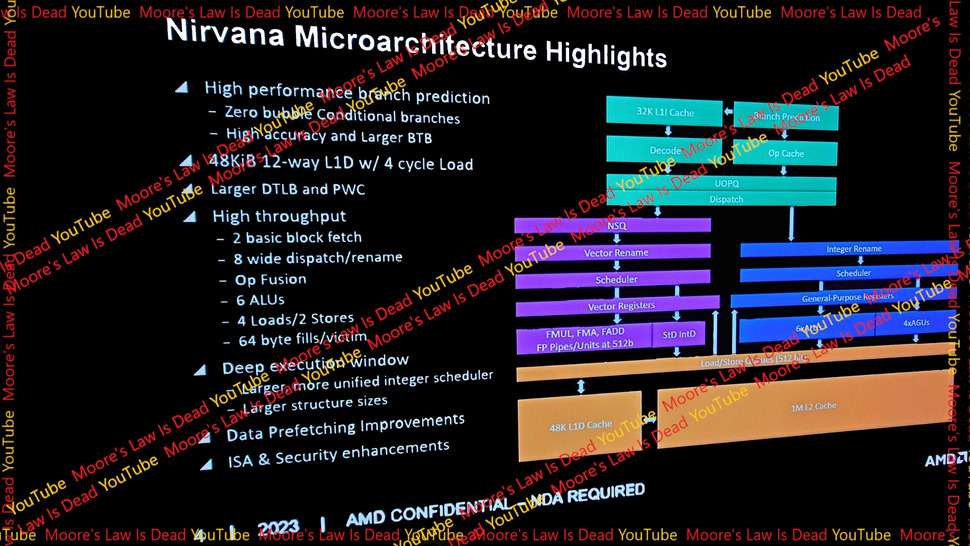

Zen 5コアに搭載される改良点のリストはかなり広範囲に及ぶ。

最大の改良点は、L1キャッシュ、分岐予測器、実行ウィンドウ、コア処理スループットだ。

分岐予測器は、ゼロバブル条件分岐、高精度、より大きなBTBを獲得した。

Zen 5のL1キャッシュ・サイズは、Zen 4の32KBからZen 5では48KBに拡大した。

チップのスループットは広範囲に改善されており、2つの基本ブロックフェッチユニット、8つのワイドディスパッチ/リネーム、6つのALU、4つのロードユニットと2つのストアユニットなどを備えているという。

また、スケジューラの構造サイズも大きくなり、整数スケジューラも以前の設計より大型で統一されているという。

このスライドには、ISAとセキュリティの強化とともに、データプリフェッチの改善も挙げられているが、具体的な詳細については触れられていない。

リークされたスライドから明らかになったもう1つの大きな改良点は、Zen 5のCCX(コアコンプレックス)のコア構成で、8個から16個に倍増している。

この新しい変更は、AMDがCCXのコア数をわざわざ増やすのはZen 2以来初めてのことで、将来的には32コアの「Ryzen 9 8950X」が登場する可能性があることを意味する。

これらの新しいZen 5コア・クラスタがどのような種類のコアを搭載するかはまだ分かっていない。

Zen 5のコア数の半分がZen 5c効率コアに特化される可能性もあるし、スタック全体がバニラZen 5パフォーマンスコアになる可能性もある。

AMDのスライドによれば、FP-512をサポートするモデルや低消費電力コアを搭載するモデルなど、さまざまなモデルが存在するようなので、その両方が混在する可能性もある。

これらのスライドは、AMDのエンタープライズ・サーバー・チップ(EYPC)を厳密にターゲットにしたものであり、メインストリームのコンシューマー向けデスクトップCPUに焦点を当てたものではないことは言及しておく価値がある。

そのため、FP-512のサポートのように、すべての詳細が来年のRyzen 8000チップに搭載されるとは思わないでほしい。

しかし一般的に、基本的なアーキテクチャ仕様はRyzen 8000に搭載される可能性がある。

リークされたスライドには、AMDのZen 6アーキテクチャに関する追加予測も示されている。

このスライドによると、Zen 6のIPC目標は最低でも10%、AI/機械学習用のFP16、新しいメモリ・プロファイラが搭載されると推定されている。

最後の箇条書きでは、AMDがCCDあたりのコア数を再び倍増させ、16コアから32コアに急増させるとしている。

この2回目のコア数倍増には、より低速でコンパクトなZen 6効率コアが含まれる可能性が高いが、それでもAMDが3世代未満でコア数を4倍にする可能性があるという事実は印象的だ。

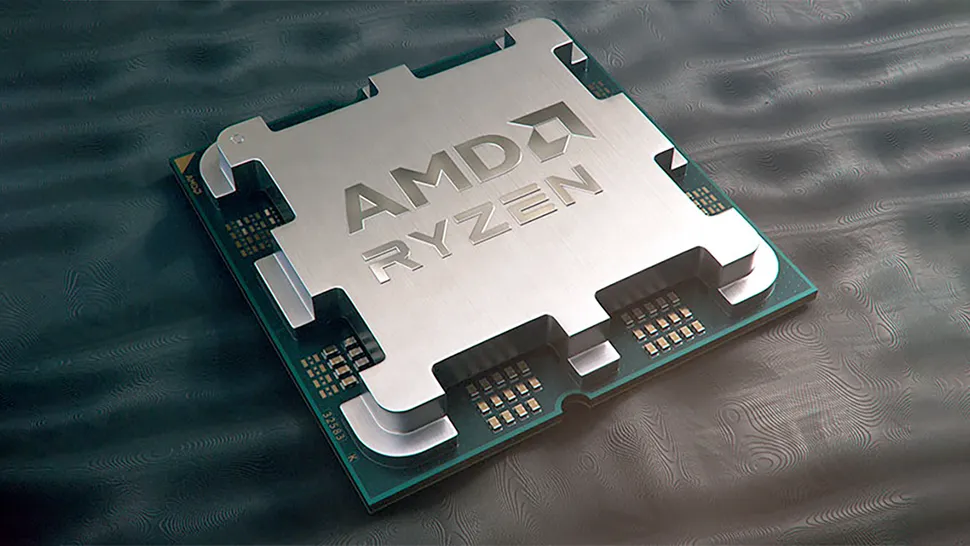

Zen 5はAMDの次世代CPUアーキテクチャで、2024年にAMDのRyzen 8000シリーズのデスクトップおよびモバイルチップでデビューする予定だ。

そして、正式発表までまだ時間があることを考えると、これらの情報はすべて塩を多量に含んだものとして受け止めなければならないことを忘れないでほしい。

ソース:Tom's Hardware - Alleged AMD Zen 5 Specs Leak: Twice the Cores, 15% Increased IPC Over Ryzen 7000

解説:

Zen5はCCXのコア数が倍増1CCXあたり最大16コアに

昨日MLIDが更新され、新しい情報が出ました。私もざっと見ました。

リークしたベンチマークによるとZen5はシングルスレッド性能の14-26%の向上が見られる。

最高30%のシングルスレッド性能向上のソースもある。

これらはIPCとされていましたが、シングルスレッド性能の間違いだと思われます。

IPC15%だとクロックによっては30%を超えるシングルスレッド性能になります。

さすがにそれは無いんじゃないかと私は思います。

1CCX当りのコアが倍増される件に関しては、コア構成は今のところ不明とのことですね。

Zen5をPコア、Zen5cをEコアとすると8P+8Eの可能性もあるし、16Eの可能性もあるということです。

MLIDでは、8Pと16Eの2種類の主要なCCDがあるとされていました。

これを組み合わせて8P+8P、16E+16E、8P+16Eのように出来るのではないかとのことです。

StrixHaloのコア構成を見ると、他に専用のグラフイックスダイがあるのではないかと思います。

当初StrixHaloの話を聞いたとき、2CCD+巨大なグラフィックスダイを搭載した専用のIODと組み合わせるのかと思っていました。

しかし、それよりも16EのCCDとStrixHalo用の2560SPグラフィックスダイと従来のIODを搭載したほうが合理的ですよね。

さらにZen6ではIPC向上率10%、AI/機械学習用のFP16、新しいメモリ・プロファイラが搭載されるとしています。

CCXは16コアから32コアに倍増されるとされており、CCX当たりのコア数は2世代で一気に4倍になる可能性があるということになります。

Ryzenはこの2世代で大きく変貌することになります。

私の予想では、何らかの形でAI/ML性能にもフォーカスしてくると思います。

これらの変化とAIEがどのように絡んでくるのかはまだわかりませんが、どこかでAI/MLワークロードに焦点を当ててくることになると思います。

最近のAI/ML周りの進化を見ているとそのように感じます。

Ryzen 9000シリーズ

Ryzen 7000X3Dシリーズ

Ryzen 8000GシリーズAPU(GPU内蔵)

Ryzen 5000/4000シリーズ