IFSは現在、ファウンドリー・ビジネスのためのテクノロジーとパートナーをすべて揃えている。

インテルは、Intel Foundry Services (IFS) Direct Connect 2024において、業界で初めてHigh-NA EUVを採用した新しい14Aノードを含む新しいロードマップを発表した。

IFSはまた、既存のプロセスノードのラインナップに新たな拡張機能を追加し、18AノードでClearwater Forestプロセッサーのウェハーを生産することを発表した。

これは、4年間で5つのノードを提供するというインテルの大胆な目標(5N4Y)が年内に完了する予定であることを証明するものであり、インテルが2025年に18AノードでTSMCからプロセスノードのリーダーの座を奪還することを確信させるものである。

マイクロソフトもまた、インテルの18Aプロセス・ノードでチップを製造すると発表した。

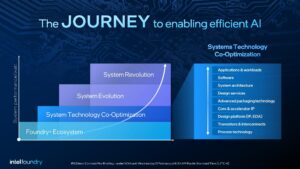

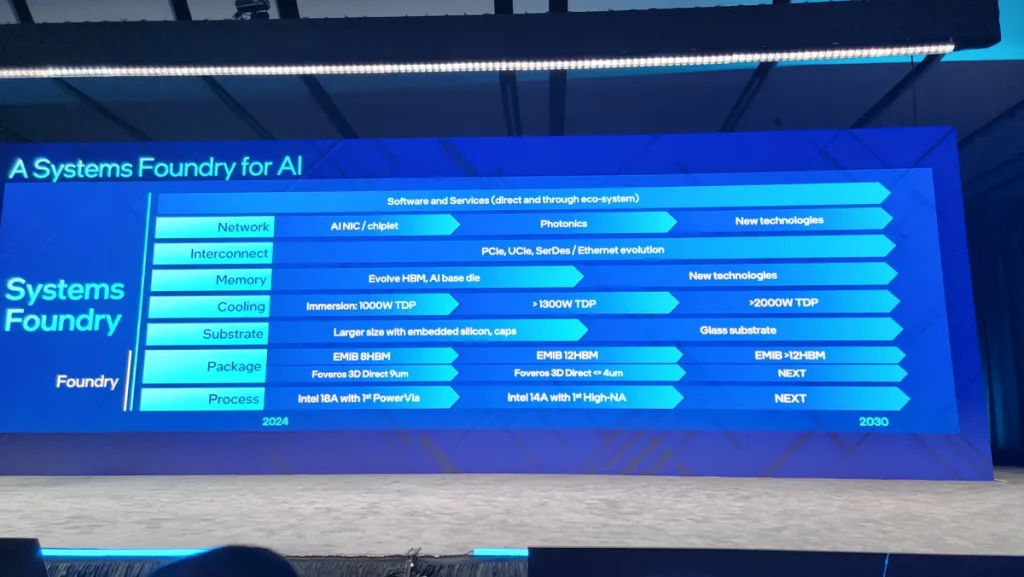

その一環として、インテルはIFSをインテル・ファウンドリーに改名した。インテル・ファウンドリーは、2030年までに世界第2位のファウンドリーになるという目標を掲げており、IFS Direct Connect 2024は、インテルが定義した「システム・ファウンドリー」としてのカミングアウト・パーティーとなる。

システム・ファウンドリーとは、システムレベルの設計に関する経験を数値化したもので、技術開発、製造、サプライチェーン、インテル・ファウンドリー・サービスのすべてを1つの傘下に含む用語である。

これには、様々なタイプのプロセッサーの製造だけでなく、パッケージングや接続性ファブリック・ソリューションの顧客への提供、さらには冷却ソリューションの支援も含まれる。

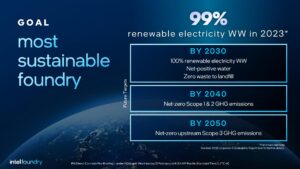

インテル・ファウンドリーは、インテル社内の外部顧客と内部顧客の両方に対応しており、弾力性があり持続可能なサプライチェーンで、両者に等しくサービスを提供することを目標としている(これは重要な違いである)。

さらに、インテルはインテル・ファウンドリーのASAT(Advanced System and Test)ポートフォリオにおける新機能を発表した。

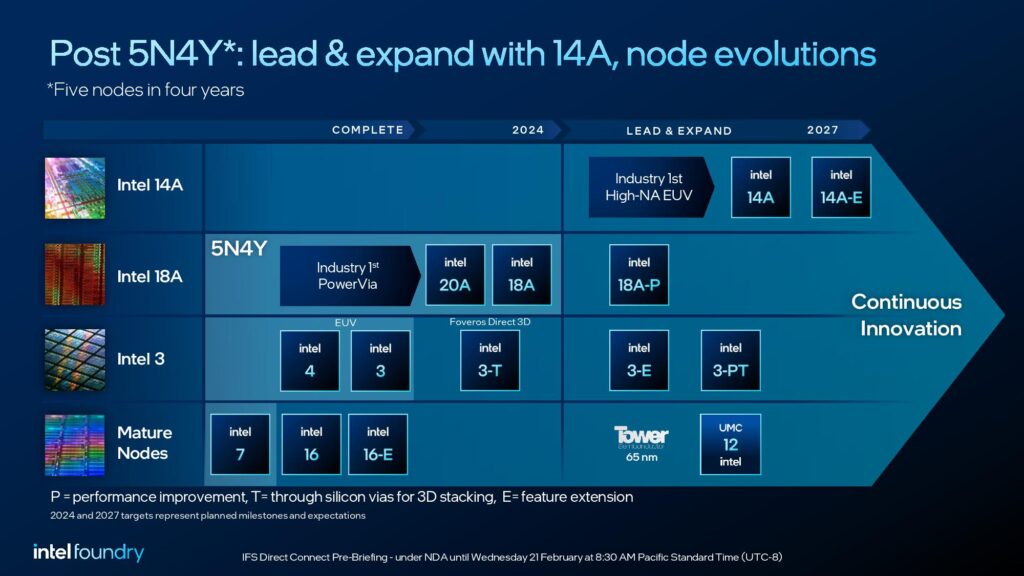

さて、ロードマップに移ろう(インテル対TSMC、サムスンのロードマップも以下に掲載)。

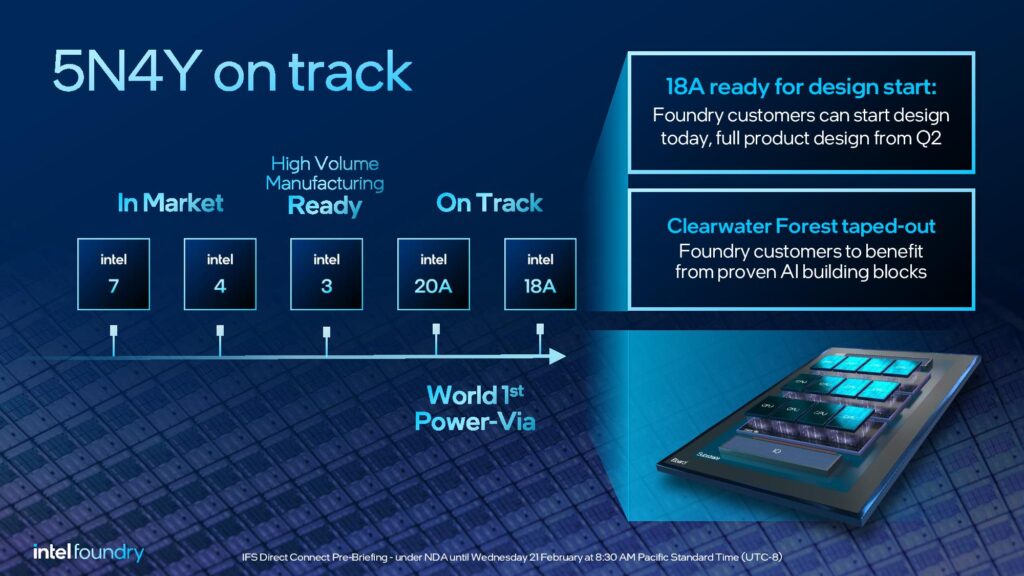

新しいロードマップについては次に紹介するが、上にあるように、インテルCEOのパット・ゲルシンガーが当初2021年に発表した4年間で5ノードを実現するという計画は、依然として予定通りである。

インテル7とインテル4ノードは現在市場に投入されており、インテル3は大量生産(HVM)の準備が整っている。

インテルの20A(2nm)と18A(1.8nm)もまた、性能とトランジスタ密度を向上させるために最適化された電源配線を提供するPowerViaバックサイド・パワー・デリバリーと、より小さな面積でより高速なトランジスタ・スイッチングとともにより優れたトランジスタ密度を提供するRibbonFETゲート・オール・アラウンド(GAA)トランジスタを搭載したインテル初のノードの両方が搭載された業界初のチップとして登場する予定である。

インテルの18Aは現在、インテルのEDA(設計ソフトウェア)およびIPパートナーから提供される0.9 PDKを使用して顧客が設計する準備が整っており、完全な1.0 PDKは4月から5月の期間に到着する。

インテルは現在、Clearwater Forestをテープアウトしており、これはチップの最終設計が生産準備に入ったことを意味する。

Clearwater Forestは、同社初の量産型18Aチップである。

上のスライドで明らかにされているように、Clearwater Forestは18Aノードで製造されたCPUタイルで構成され、3D Foverosパッケージング技術を使ってIntel 3ベースダイと結合される。

ベースダイにはキャッシュも含まれている。

Clearwater Forestの設計には、Granite Rapidsや288コア、144コアのSierra Forestプロセッサで見られたアーキテクチャコンセプトの多くが盛り込まれているが、新たに追加された3D Foverosパッケージングが鍵となる。

ロジック・ダイとベース・ダイを接合するこの戦術は、HBM4を使用するチップ設計においても重要であり、最適なシグナル・インテグリティを確保するためにアクティブなベース・ダイが必要になると聞いている。

このように、この技術は、メモリ帯域幅を必要とするAIチップの次の波にとって非常に重要になるだろう。

Clearwater Forestは、チップ同士を接続する新しい業界インターフェースであるユニバーサル・チップレット・インターコネクト・エクスプレス(UCIe)を採用した初の量産チップである。

UCIeは、インテル、AMD、Arm、Nvidia、TSMC、サムスン、その他120社によってサポートされており、チップレット間のダイ間相互接続をオープンソース設計で標準化することで、コストを削減し、複数のチップメーカーのチップレットを組み合わせて検証する幅広いエコシステムを育成する。

インテルがClearwater ForestのためにUCIeと全面的に取り組んだことは、この技術が急速に進展していることを示すだけでなく、インテルが業界をリードしていることを示すものでもある。

5N4Yを越えて - インテル14Aとカスタマイズ・ノード・エクステンションの登場

ポスト5N4Yチャートは、次に何が起こるかを示している-インテル14Aプロセスである。

これは、ASMLのHigh-NA EUVリソグラフィ・ツールを使用する業界初のプロセス・ノードとなる。この新しいチップ製造ツールにより、チップメーカーはこれまでよりも小さなフィーチャーをプリントできるようになり、インテルはより高い性能を実現できるとしている。

実際、最先端のHigh-NAツールの提供を受けるのはインテルが業界で初めてであり、TSMCはコスト面の懸念から2030年までツールの使用を延期すると言われている。

インテル・ファウンドリーの責任者であるStu Pann氏は、このツールはインテルの目的にとって費用対効果が高いと語っており、この件に関するASMLのコメントと同じである。

インテルは、競合他社にまだ目標を与えたくないとして、14Aの性能や密度の目標をまだ共有していない。

しかし、次世代PowerViaバックサイドパワーデリバリー(おそらくSource-on-Contact)とRibbonFET GAAトランジスタが搭載されることは分かっている。

インテルのロードマップには、標準的な14Aと、14A-Eと呼ばれる後続の拡張機能という2種類の14Aがある。

Eは機能拡張を意味し、TSMCやサムスンのように、既存のプロセスノードをさまざまにカスタマイズして提供し、ライフサイクルを延長するというインテルの新しいアプローチの一部である(詳細は後述)。

インテルは、最初の14Aリビジョンの日付を確約していないが、2024年以降に登場することは分かっている。

2回目の14A-Eリビジョンはリスク生産に移行し、最初のテストチップは2027年にA0シリコンで製造されることになる。

インテルがTick-Tockのようなペースに戻ることと、14A-Eのタイミングを考えると、14Aは2026年に登場すると考えていいだろう。

インテルの他の最先端ノードと同様、14Aはオレゴンで開発され、その後他の施設(現時点では未定)で量産される。

インテルはまた、インテル7、インテル3、インテル16ノードを新しい「ライン・エクステンション」で拡張する。

インテルは、2年ごとに新しいノードを提供し、1年おきにライン拡張を行うことを計画している。

これらのライン拡張は、新しい接尾辞で示される。

Pサフィックスは性能向上を伴うノードの新リビジョンを示し、Tサフィックスはハイブリッドボンディング/3D Foverosで使用可能なTSV搭載ノードを示し、Eサフィックスは動作/電圧範囲の調整など特殊な新機能を示す。

インテルはまた、性能と特別な機能の両方を示すPTリビジョンも用意しており、時間の経過とともに他の複合リビジョンも出現すると予想される。

この手法により、インテル・ファウンドリーは既存のノードをさらに活用し、特定の顧客のユースケースに対応できるようになる。

インテルはまた、UMCとの新たな製造協力の成果として、新しいインテル12ノードを数年内に登場させる予定だ。

インテル・ファウンドリーはまた、タワー・セミコンダクター向けに成熟ノードの65nmチップを製造している。

これらの協業はいずれも、インテルのIFS事業の規模をさらに拡大する鍵であり、同時に同社は、すでに減価償却済みのツールや設備からより多くの価値を引き出すことができる。

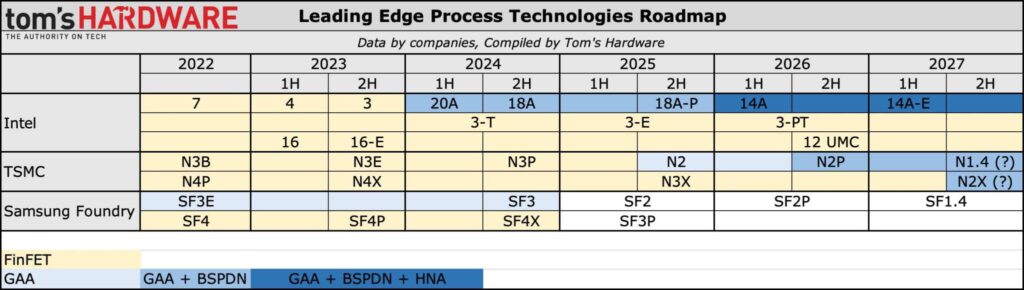

インテル vs TSMC vs サムスン プロセス・ノード・ロードマップ

上記のロードマップは一般に公開されている情報に基づいていますが、最も重要なPPAC(Power、Performance、Area、Cost)指標のいくつかは含まれていないことに注意してください。

しかし、インテル、TSMC、サムスンの将来的なプロセス・ノードのタイムラインは示されている。

また、TSMCとサムスンも、現在のインテルと同様に、同じノードの複数のライン拡張を使用していることがわかる(例えば、TSMCのN3B、N3E、N3P)。

サムスンは2022年にゲート・オール・アラウンド(GAA)トランジスタを初めて市場に投入したが、その実装はあまり性能が高くなく、歩留まりの悪さに苦しみ、TSMCに市場シェアをさらに奪われる結果となった。

これはまた、技術があれば必ず成功するとは限らないこと、つまり実装が重要であることを浮き彫りにしている。

インテルの20Aと18Aには、GAA(PowerVia)とバックサイド・パワー・デリバリー・ネットワーク(BSPDN)の両方が搭載されており、インテルはTSMCより2年半早くバックサイド・パワー・デリバリーを実現し、GAAでもTSMCより1年半早く市場に投入することになる。

最先端ファウンドリ業界のダークホース的存在であり続けるサムスンに見られるように、これらの技術を持っているからといって必ずしも勝利が約束されるわけではない。

しかし、重要なPPAC指標が正しく一致すれば、インテルがこれらの技術を早期に採用したことで、TSMCに対して大きな優位性が生まれるだろう。

最後に、見てわかるように、14Aはインテル・ファウンドリーが最先端のHigh-NA EUVリソグラフィ装置を使用する最初のファウンドリーであることを示す。

ある業界レポートによると、High-NA方式はデュアルパターニングによるLow-NA EUV方式ほど費用対効果が高くない。

インテルは、コスト指標は想定内に収まると確信しているが、当然ながら、必要であれば戦略を調整すると述べている。

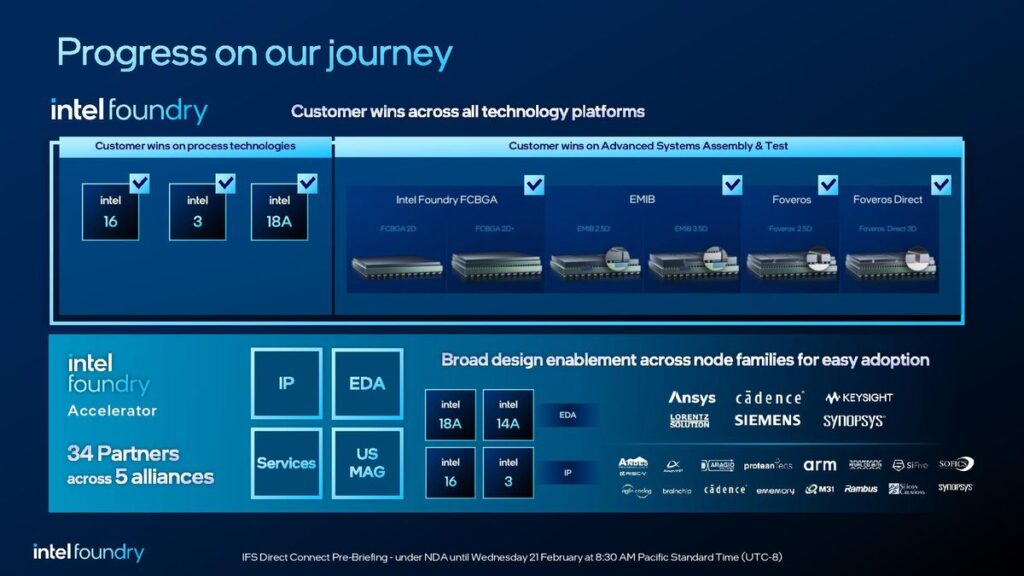

EDAチップ設計ソフトウェアとパッケージング・オプション一式

インテルは、2023年に4つの大規模な18A顧客コミットメントを確保した。

マイクロソフトもインテルの18Aプロセスでチップを製造すると発表しており、これは業界最大手の1社からの大きな賛同である。

また、インテルは、インテル16およびインテル3ノードでデザインウィンを獲得しており、インテルファウンドリーASATパッケージングサービスでは、EMIB、Foveros、Foveros Directとの有利なアドバンスドパッケージング契約を含む重要な契約を獲得している。

インテル・ファウンドリー・サービス・アクセラレーター・プログラムは、チップ設計者や企業がインテルの製造技術を容易に採用できるよう支援する。

このプログラムには、4つのアライアンスにまたがる34のパートナーが参加しています: IP、EDA、設計サービス、USMAG(米軍、航空宇宙、政府)の4つのアライアンスにまたがる34のパートナーが含まれています。

この幅広いパートナーには、Ansys、Cadence、Synopsys、Siemens、KeysightなどのEDA業界の重鎮や、Arm、RISC-V、SiFive、Rambusなどの幅広いIPパートナーが含まれる。

感想

※ 画像をクリックすると別Window・タブで拡大します。

インテル18Aは、同社がTSMCに対するプロセス・ノードの優位性を取り戻すターニングポイントとなることを意味しており、すべての外見上の兆候は、このノードがしっかりと軌道に乗っていることを示している。

インテル対TSMC対サムスンのファウンドリ・ロードマップで述べたように、インテルは自社のプロセス・ノードにバックサイド・パワー・デリバリを最初に組み込み、技術面でTSMCを大きくリードすることになる。

インテルはTSMCより2年半早くバックサイド・パワー・デリバリーを実現し、GAAでもTSMCより1年半早く市場投入することになる。

重要なPPAC指標が正しく一致すれば、インテルはこれらの技術を早期に採用することで、大きなアドバンテージを得ることになる。

前節で述べたように、インテル・ファウンドリーは、すべてのファウンドリー製品で顧客から大きな成功を収めている。

マイクロソフトもインテルの18Aプロセスでチップを製造すると発表しており、業界最大手の一社から大きな賛同を得ている。

インテルはまた、チップのパッケージングとテストにおいて広範な経験を持っており、顧客向けの最先端パッケージング技術の印象的なポートフォリオも持っている。

最近、マレーシアのペナンにある同社のパッケージング施設を視察した際、私たちが実際に目にしたように、AIチップのパッケージング契約が急激に増加している。

インテルのパット・ゲルシンガー最高経営責任者(CEO)は最近、5年前はパッケージングが最先端プロセッサーの総コストの15%を占めていたが、現在は35~40%に跳ね上がったと指摘した。

このように、インテルのパッケージング・ビジネスの進歩は、特に、同社のチップ製造サービスも利用することを選択するかもしれない顧客との新たな関係を確立するのに役立つことを考えると、無視できない。

また、インテル・ファウンドリーはアーム社と提携し、Neoverse・チップを同社のファウンドリーに供給している。RISC-V社やSiFive社などとの既存のパートナーシップは言うまでもない。

インテルのEDAおよびIPパートナーの広範なポートフォリオは、インテル・ファウンドリの顧客に業界標準の設計ツールを提供することになり、企業がインテル・プロセス・ノードを迅速に採用するための容易なオンランプを提供します。

豊富なプロセス・ノードと幅広いパッケージング・サービスに加え、システム・レベルの設計経験を持つIFS社は、今後数年間、TSMC社やサムスン社とサード・パーティ・ファンドリーの顧客を獲得するために熾烈な競争を繰り広げる態勢を明らかに整えている。

こうした取り組みについては、2030年までにインテル・ファウンドリーを世界第2位のファウンドリーにすることを任務とする、インテル・ファウンドリー・サービス担当SVP兼GMのステュー・パン氏へのインタビューで詳しく読むことができる。

解説:

インテルFab復活の兆し

Intel18Aの次、Intel14Aの話が上がっています。

対するtSMCはコスト的な懸念と世界経済の減速で2nmを2025年から2026年に遅らせるとのことですから、対照的です。

そもそも半導体の製造は、顧客がどのくらいとってこれるかも重要で、18Aの顧客は自社のほかにも確保できているようですので、問題なさそうです。

intelはパッケージング技術で先を行ってTSMC2nm以上の性能があると自信を持っているようですね。

このまま行ったらnVIDIAやAMDもIntelのFabでチップを作る可能性が出てくるのかなと思わせる話です。

2nm前後からまたしてもIntelのFabが復活してくるかもしれません。

わたくしは以前のようなIntelがFabの力を使って猛威を振るうような状態は好まないので、できればTSMCにもう少し頑張ってほしいところです。

コスト的な懸念を全てクリアして、2nm以降のプロセスを早々に予定に挙げてくるのはさすがIntel様といったところです。

Intelが最先端のプロセスを他社に開放するのかどうか、注目したいところです。