AMDの第2世代EPYC Romeプロセッサは8月に発売され、それ以来、チップ自体とその機能についての詳細を取得しています。

拡大ダイショットを含むI/Oダイの最新の詳細は、Hardwareluxxによって明らかにされており、これまでにAMDの最も革新的なサーバーチップをよりよく見ることができました。

AMD第2世代EPYC RomeプロセッサIODの詳細-シングルダイで834億個のトランジスタ、チップ全体で39.54億個のトランジスタ

AMDが最近、第2世代EPYC Romeプロセッサ向けに明らかにし始めた多くの詳細がありました。

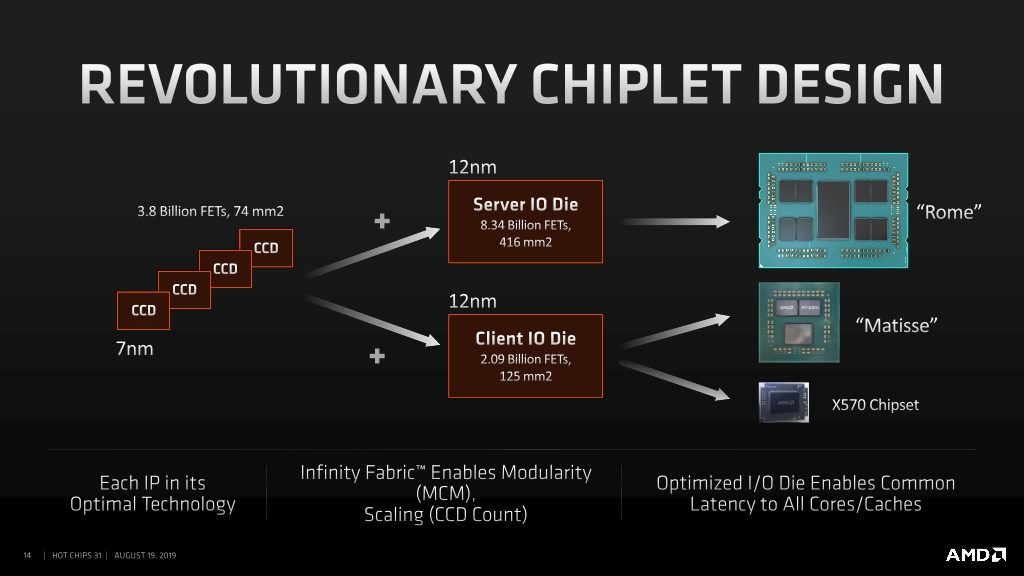

AMD EPYC Romeプロセッサは9ダイ設計で構成されており、MCM(Multi-Chip-Module)とも呼ばれます。

9つのダイには、8つのCCD(演算コアダイ)と1つのIOD(入力/出力ダイ)が含まれます。

各CCDは、それぞれ独自のL2キャッシュと共有L3キャッシュを備えた4つのZen 2コアを備えた2つのCCX(Compute Core complex)で構成されています。

8つのCCDはすべて、インフィニティ・ファブリックを使用してI/Oダイに接続されています。

各CCDは74mm2で、39億個のトランジスタで構成されています。

Ryzenに搭載されているIODのダイサイズは125mm2で、20億900万個のトランジスタで構成されています。

EPYCに搭載されているIODは、834億個のトランジスタで構成され、416mm2で測定されます。 これは、第2世代EPYCチップの最大のダイです。

IODは、1005mm2の8 Zen 2 CCDと組み合わされ、395億4千万個のトランジスタで構成されています。

現在、Rome搭載されているIODは、Ryzenプロセッサに搭載されているIODよりもはるかに大きくなっています。

これは、サーバープラットフォームのより厳しい機能セットによるものです。

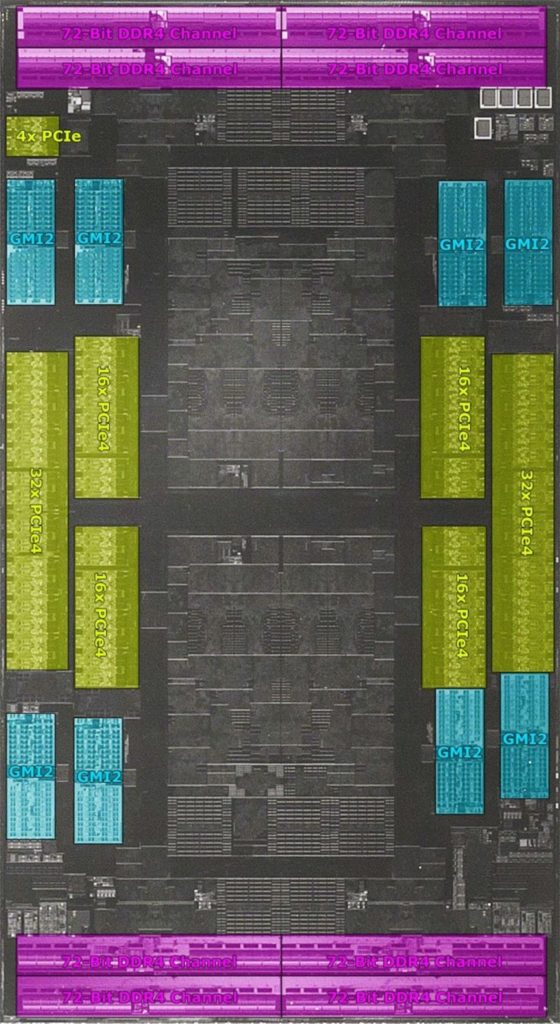

透光を使用して露出すると、IOダイがはっきりと露出し、内部ブロックが非常にはっきりと見えるようになります。

IODの中央スペースの多くはSRAMとクロスバースイッチ専用であり、PCIe Gen 4インターフェースはIODの側面にあると述べられています。

ダイの上部領域と下部領域は、4つの72ビットDDR4メモリチャネルを備えています。

ここからが興味深い部分です。EPYC2nd Genは、PCIe Gen 4で2倍の帯域幅を提供し、Infinity Fabricのバスへの依存を減らすことで162個のPCIeレーンまで拡張できます。 。

追加のPCIeレーンはすでに存在しますが、インターコネクトによって使用されています。

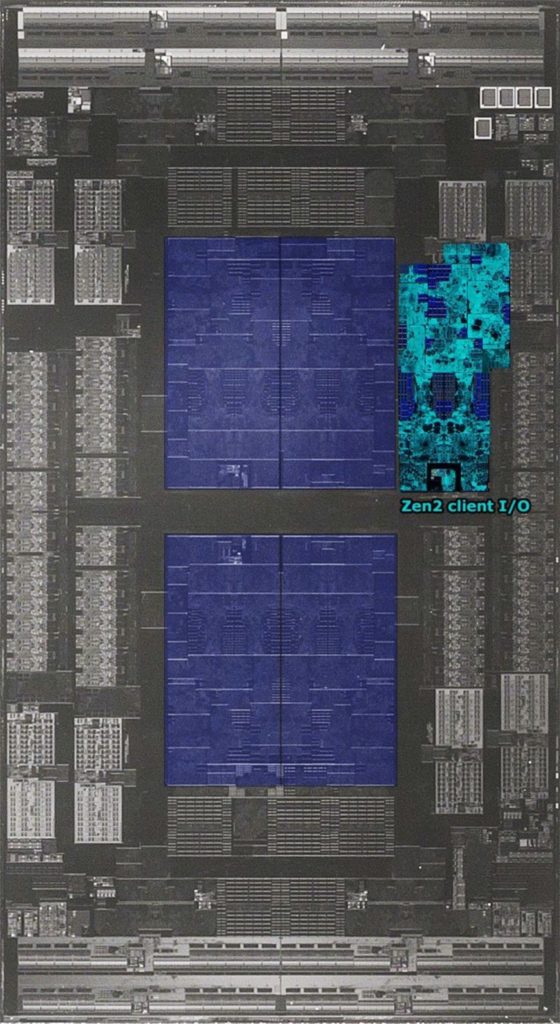

IODに加えて、Zen 2 CCDまたはCompute Core DieもFlickrのOC_Burnerから独自のダイショットを受け取りました。 まだ見たことがない人のために、Ryzenプロセッサーの各コアダイは次のようになっています。

同じダイが、Zen 2ベースのRyzen、EPYC、および今後のRyzen Threadripperプロセッサで使用されています。

また、EPYCプロセッサのIODは、RyzenプロセッサのIODと比較され、サーバー向けIODがどれだけ大きなチップであるかが明らかになります。

AMDは、さまざまなコアカウントに基づいて、さまざまな第2世代EPYC Romeプロセッサをどのように構成するかについて既に説明しました。

すべてのEPYC Romeチップには合計8つのCCDがありますが、多くのプロセッサーですべてが有効になっているわけではありません。

AMD第2世代EPYC Rome CCD構成とSOCアーキテクチャのブロック図(画像クレジット:Planet3DNow):

16コアモデルなど、一部のCCDでさえ部分的に無効にする必要があります。

16コアモデルでは4つのCCDのみが有効になっており、各CCDは4つのコアで部分的に有効になっています。つまり、各CCXで有効なコアは2つだけです。

一部のCCDではCCXごとに3つのコアが有効になっていますが、48コアバリアントなどでは8つのCCDすべてが有効になっていますが、CCDの2つでは4つのコアすべてが有効なCCXと3つのコアのみが有効なCCXがあります。

AMD CPU ロードマップ (2018-2020)

| Ryzen世代 | Ryzen 1000 Series | Ryzen 2000 Series | Ryzen 3000 Series | Ryzen 4000 Series | Ryzen 5000 Series |

| アーキテクチャー | Zen | Zen/ Zen+ | Zen2 | Zen3 | Zen4 |

| 製造プロセス | 14nm | 14nm / 12nm | 7nm | 7nm+ | 5nm/6nm? |

| ハイエンドサーバー (SP3) | EPYC 'Naples' | EPYC 'Naples' | EPYC 'Rome' | EPYC 'Milan' | EPYC 'Next-Gen' |

| サーバー最大 コア数/ スレッド数 | 32/64 | 32/64 | 64/128 | 不明 | 不明 |

| ハイエンド デスクトップ(TR4) | Ryzen Threadripper 1000 Series | Ryzen Threadripper 2000 Series | Ryzen Threadripper 3000 Series (Castle Peak) | Ryzen Threadripper 4000 Series | Ryzen Threadripper 5000 Series |

| HEDT最大コア数/ スレッド数 | 16/32 | 32/64 | 64/128? | 不明 | 不明 |

| デスクトップ (AM4) | Ryzen 1000 Series (Summit Ridge) | Ryzen 2000 Series (Pinnacle Ridge) | Ryzen 3000 Series (Matisse) | Ryzen 4000 Series (Vermeer) | Ryzen 5000 Series |

| 最大コア数/ スレッド数 | 8/16 | 8/16 | 16/32 | 不明 | 不明 |

| GPU内臓 | 無し | Ryzen 2000 Series (Raven Ridge) | Ryzen 3000 Series (Picasso 14nm Zen+) | Ryzen 4000 Series (Renior) | Ryzen 5000 Series |

| 発売年 | 2017 | 2018 | 2019 | 2020 | 2021? |

しかし、これはほんの始まりに過ぎません。AMDは、それぞれZen 3およびZen 4コアアーキテクチャを使用するコードネームEPYC MilanおよびEPYC Genoaの次世代サーバープロセッサで、より高度なパッケージングとチップレットデザインを使用することが期待されています。

今後数年間でAMDとその長期的なZenロードマップがすべて順調に動作する場合、CPU市場のすべてのセクターを再び支配していることがわかります。

AMDのEPYC RomeはすでにAmazon(AWS)との主要な取引を確保しています。

また、Atos BullSequana XH2000スーパーコンピューターに電力を供給する7nm Romeプロセッサーを提供し、米国エネルギー省が構築し、2021年に展開を目指すフロンティアスーパーコンピューターに次世代のEPYCラインが電力を供給する予定です。

解説:

EPYC Romeのダイショットが公開されました。

Ryzen3000と比較しても巨大なダイで特にI/Oダイが巨大になっているとのこと。

Threadripperもおそらく似たような感じになるのではないかと思います。

そういう考えもあってこの記事を翻訳してみました。

私も写真を見たとき、演算用ダイより巨大とは思っておらず、びっくりしました。

Zen2はIPCの向上もさることながらPCI Express4.0の対応のI/O性能の強化に如何にトランジスタが費やされたかがよくわかるのではないかと思います。

来月いよいよ新Threadripperが発売されます。

これまでになかった性能がいよいよ一般に下りてくることになります。