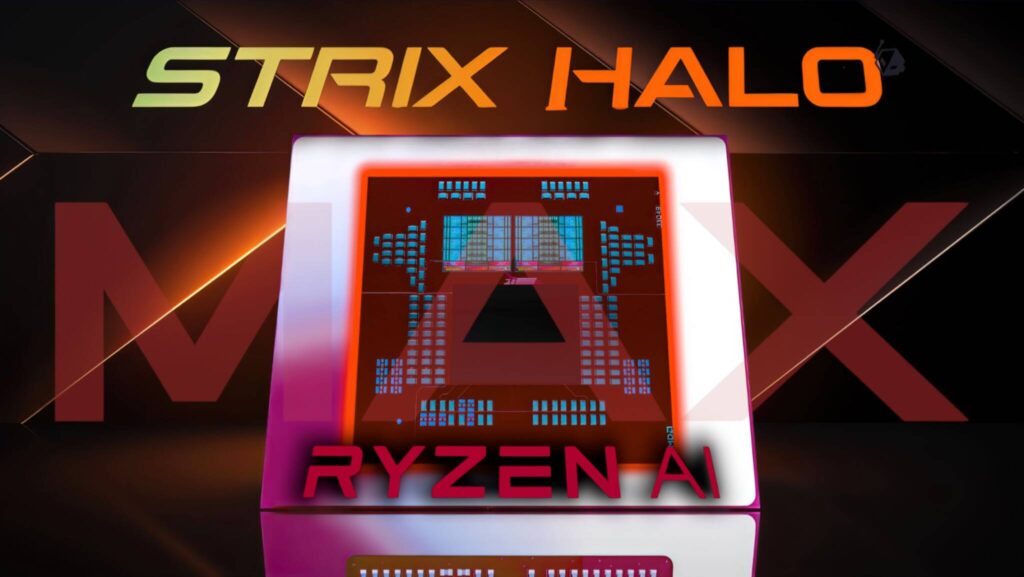

AMDの「Strix Halo」CPUは、ダイ設計に見られるように、3D V-Cache技術による追加のL3キャッシュをもたらす可能性がある。

より新しいインターコネクト設計とは別に、AMDのStrix Haloは3D V-Cache技術による追加のL3キャッシュをもたらすかもしれない。

AMD Strix Haloのレビューが正式に発表され、再びAMDがiGPU性能の面でIntelを大きくリードしていることが明らかになった。

インテルがArrow Lake-HやLunar Lakeなどのラインナップでかなり健闘しているのは間違いないが、AMDのStrix Haloは打ち負かすのが難しい新たなベンチマークを設定している。

とはいえ、一般的なコンピューティングやゲームではすでに非常に優れているにもかかわらず、AMDはここで止まらないかもしれない。

現在のStrix Haloのダイ設計(ASUS中国経由)には、近い将来の大幅な性能向上の道を開くヒントがいくつかある。

ASUSの中国担当ゼネラルマネージャー・トニー氏が確認したように、Strix Haloはダイ設計からわかるようにTSV(Through-Silicon Vias)を搭載している。

このTSVにより、AMDはZen 5コア間のL3キャッシュのすぐ上に3D V-Cacheチップレットを追加することができる。

これにより、L3キャッシュ・メモリが追加され、特定のワークロードにおいてCPUのパフォーマンスが大幅に向上します。これにより、近い将来、Strix Halo X3Dプロセッサーへの道が開かれることになります。

TSV とは別に、Strix Halo ダイには、デスクトップ Zen 5 Ryzen 9000 CPU のインターコネクト・システムよりも省スペースな新しいインターコネクトも搭載されています。

Ryzen 9 9950Xのダイを見ればわかるように、チップはチップレット間のデータ転送に従来のSERDES(シリアライザー/デシリアライザー)を使用している。

トニーの説明によると、新しいインターコネクト設計は、全体のフットプリントを42.3%削減し、その結果、Strix Halo CPUではチップレットが0.34mm小さくなりました。

このインターコネクトは本質的に「ワイヤーの海」であり、CCDのサイズを縮小するだけでなく、レイテンシーを向上させ、消費電力を削減します。

これはZen 6のための良い基盤を確立するものだが、Strix Haloにすでに搭載されているのを見ると、エキサイティングだろう。

Ryzen AI Max+ 395のようなStrix Haloチップは、数字を計算し、集中的なワークロードを実行するにはすでに十分強力だが、そのRadeon 8060Sは別格だ。これはすでにGeForce RTX 4070ラップトップGPUと競合しており、Strix HaloラップトップはディスクリートGPUを必要とせずにウルトラ設定でゲームをプレイすることができる。

解説:

Strix HaloにはTSVが採用されている。

TSVとはThrough-Silicon Viasのことで、メモリーチップを積層して大容量を実現する技術です。

またチップ間のインターコネクトを新設計しており、ダイのサイズも小さくなっているとのこと。

元記事二枚目の画像を見ると確かに小さくなっています。

注意してほしいのはI/Oではなく0#CCD、1#CCDの方です。

I/Oに関してはRadeon 8060Sの部分が大きいですから、当然大きくなっています。

Strix HaloはTSVを採用していることによってX3Dにもできるとのことで、AMDにとっては特別の意味を持つ虎の子の製品ということになります。

iGPUの世代はRDNA3.5と最新ではありませんが、次世代の製品が出るとしたらRDNA4は飛ばしてUDNAになるのでしょう。

この分野ではMediatekと協業しているNVIDIAよりも進んでいるのでしょうから、Strix Haloが自作市場に降りてくることや続く製品では更なる性能向上を期待したいところです。

Copilot+の勝ち組製品はLunarLakeですべてそちらにかっさらわれてしまった感がありますが、Strix HaloやBald Eagle PointもiGPU用の大容量キャッシュを搭載し、それまでとは次元の違う性能を発揮できそうです。

Ryzen 9000シリーズ

Ryzen 7000X3Dシリーズ

Ryzen 8000GシリーズAPU(GPU内蔵)

Ryzen 5000/4000シリーズ