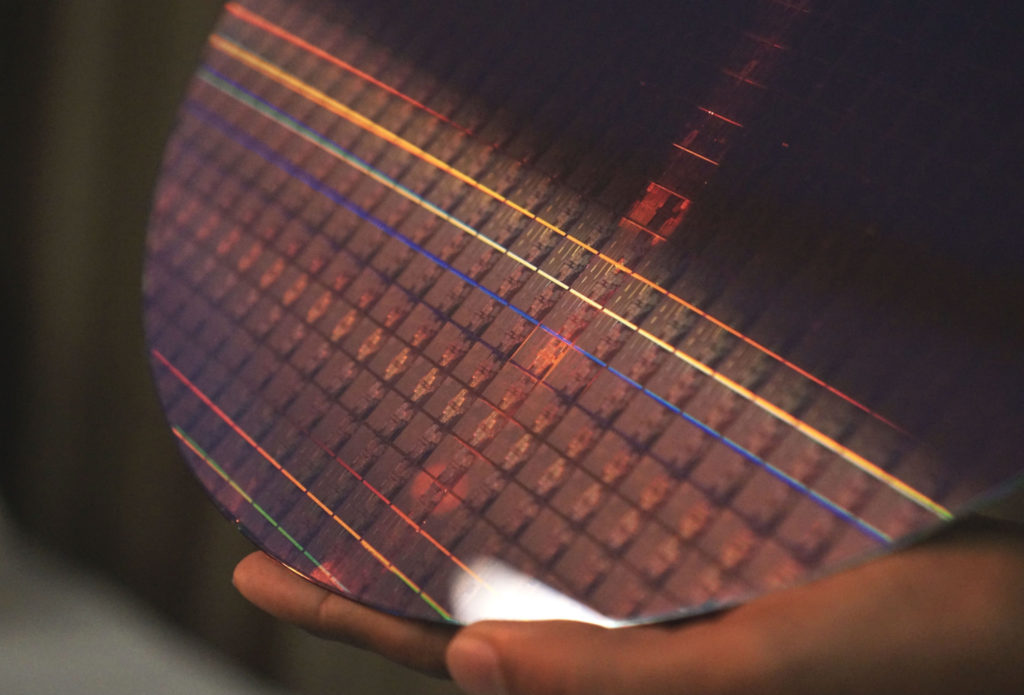

インテルは5月にプロセスロードマップを発表し、2023年までの目標計画を強調しましたが、2029年までのプロセスロードマップパスを示す詳細な製造ロードマップがアナンドテックによって明らかにされました。

次の10年間のインテル製造ロードマップ-2021年に7nm、2023年に5nm、2025年に3nm、2027年に2nm、2029年に1.4nm、ブランドの新機能とバックポート

このスライドは、9月にIntel自身が最初に発表したと述べたIntelのパートナーの1つによって、IEEE International Electron Devices Meetingで発表されたロードマップです。

インテルはすでに7nmプロセスプランの詳細を提供してくれましたが、このスライドはそれよりもさらに進んでいます。

これは今後の10年間のロードマップです。今後数年間でインテルが提供するものを見てみましょう。

※ クリックすると別Window・タブで開きます

今後10年間で10nm〜1.4nm

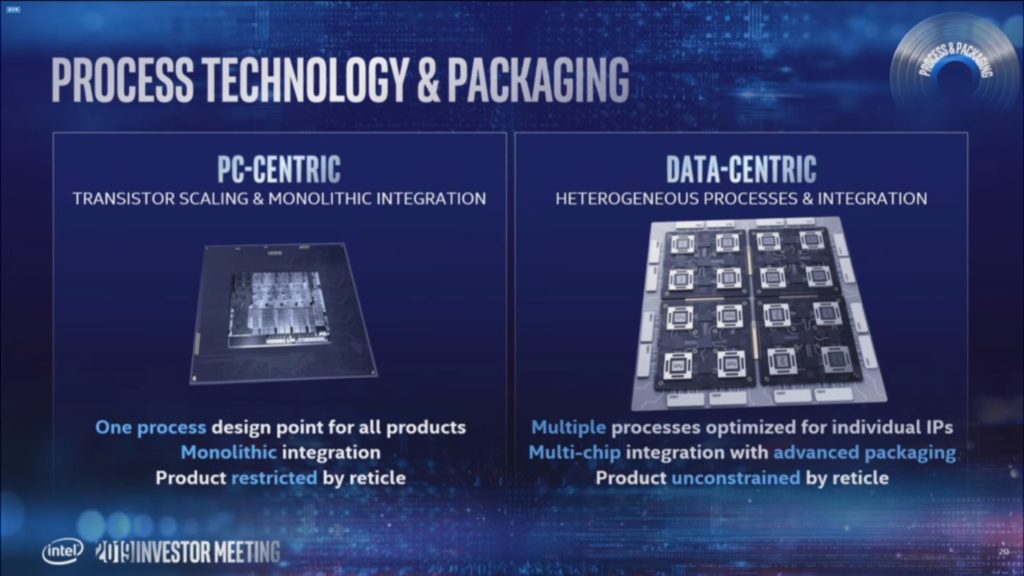

プロセスロードマップから始めて、Intelは各メジャーノードの更新について2年間の歩調を追っています。

2019年に10nm(10nm +)のソフトローンチがあり、2021年に7nm、2023年に5nm、2025年に3nm、2027年に2nm、2029年に1.4nmが続きます。

ここで興味深いのは、この2年間のサイクルがIntel自身によって最適なコストパフォーマンスパスと呼ばれていることです。

そのため、Intelはこの道に従うことを優先しますが、既存のノードでパフォーマンスを活用し、スケーラビリティを高めることができる+ / ++ノードの年次サイクルもあります。

各プロセスの最適化されたノードについて説明する前に、各主要ノードの更新が提供する主要な機能に注目する必要があります。

Intelは、7nmの最大の特徴は、EUV(極端紫外線リソグラフィー)技術を使用して作られていることだと言っています。

同様に、他のすべての主要ノードには新しい機能が搭載されますが、Intelは期待できる新しい機能を明示的に述べていません。

インテルが10nm ++製品を導入すると同時に、次世代の7nmプロセスノードの生産と発売も計画されています。

10nmおよび7nmノードは、2019年の投資家会議でIntelによって既に詳細に説明されています。

※ クリックすると別Window・タブで開きます

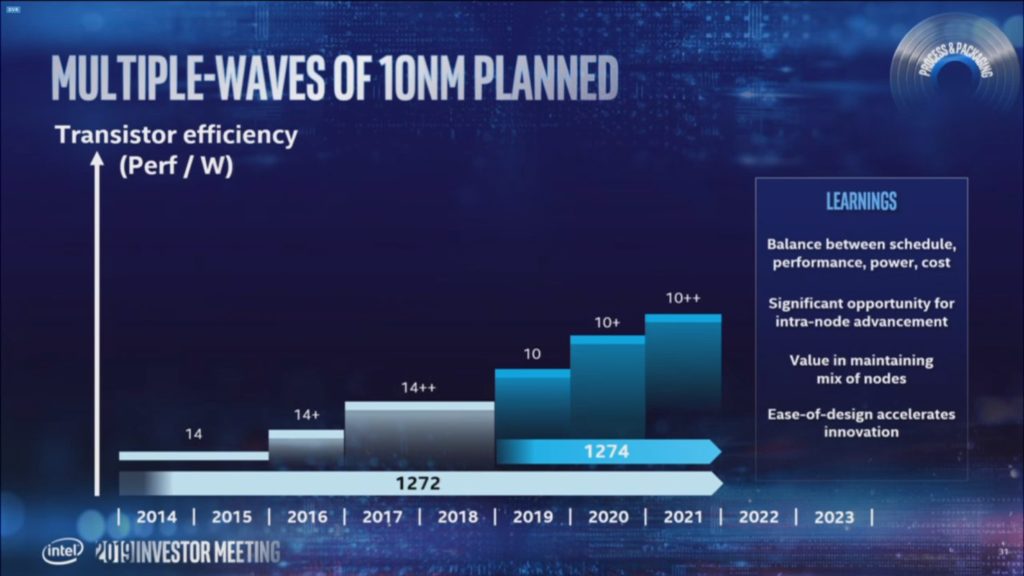

Intel 10nm、10nm +および10nm ++

10nmファミリから始めて、Intelは、10nmプロセスノードがワットあたりのパフォーマンスを大幅に向上できることを明らかにしました。

14nm ++と比較して、10nmの最初の反復は効率の良い飛躍であることが示されており、インテルは2019年に10nm +、2020年に10nm ++、2021年に10nm +++で前進する10nmの改良版を提供する計画です。

10nmが提供する主要なアップグレードには次のものがあります。

- 14nmに対して2.7x密度

- 自己整合クワッドパターニング

- アクティブゲート上の接触

- コバルト相互接続(M0、M1)

- 第一世代Foveros 3Dスタッキング

- 第2世代EMIB

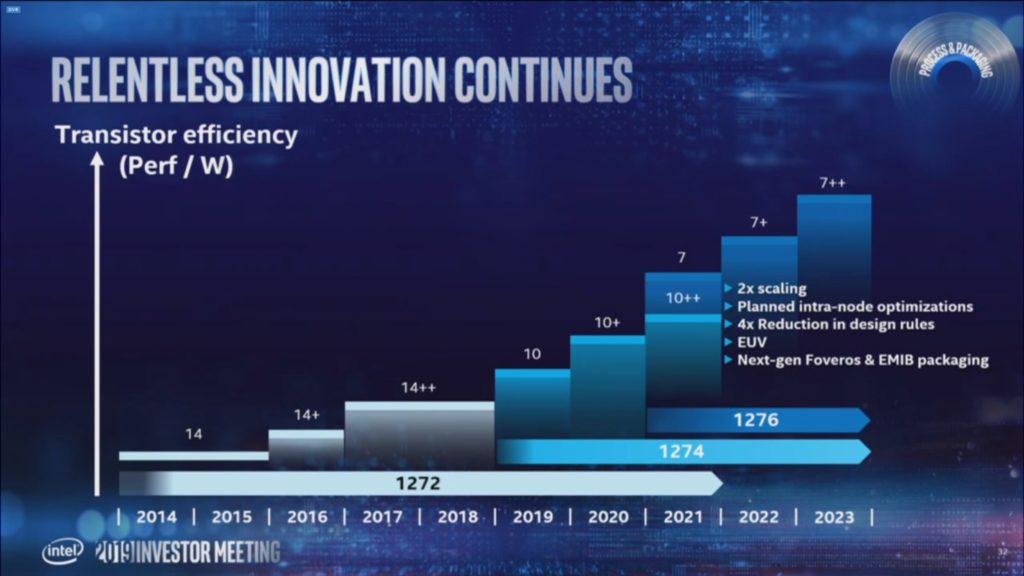

Intel 7nm、7nm +および7nm ++

インテルが10nm +++製品を導入すると同時に、次世代の7nmプロセスノードの生産と発売も計画されています。

Intelは、2022年に7nm +、2023年に7nm ++で7nmプロセスノードの最適化を引き続き提供します。

10nmと同様に、7nmは10nmを超える優れた機能強化リストを提供します。

- 2x密度スケーリングと10nm

- 計画的なノード内最適化

- 設計ルールの4倍の削減

- EUV

- 次世代FoverosおよびEMIBパッケージ

10nmは、2019年に既に10nm +上にあるため、+++最適化を行う唯一のプロセスであることに注意してください。

2029年の1.4nmは非常に有望であるように見えますが、Intelは2015年までに10nm、2017年までにnmを取得するという以前のロードマップを持っています。

しかし最近、インテルのCEOボブ・スワンは、彼の会社はすべて最初の7nm製品は2021年第4四半期までにTSMCの5nmに取り組み、2024年後半にはTSMCの3nmノードに相当し、2025年には製品が入手可能になると述べており、TSMCに対抗する準備ができていると述べました。

います。

各テールエンド最適化ノードへの改良・移植

このスライドでは、14nmおよび10nmノードを取り巻くすべての混乱を考慮して、ここ数か月で議論する興味深いトピックの1つであるバックポーティングについても説明しています。

各主要ノードには、少なくとも2つの最適化が含まれていることが示されています。

10nm +は10nm ++および10nm +++、7nmは7nm +(2022)と7nm ++(2023)、5nmは5nm +(2024)と5nm ++(2025)、3nmは3nm +(2026)と3nm ++(2027)、2nmは2nm +(2028)と2nm ++( 2029)をそれぞれ改良します。

1.4nmの最適化されたパスは言及されていませんが、このスライドも10年のロードマップのみを対象としているため、1.4nmの最適化されたノードパスも予想できません。

したがって、各主要ノードの後には、来年に最適化された「+」ノードが続き、その後にさらにテールエンドに最適化された「++」ノードが続きます。

興味深いのは、「++」または10nmの場合は+++ノードが次のメジャーノードと一緒に起動することです。

最適化されたノードには、以前の2つの更新からの頻度やスケーラビリティなど、新しいノードよりも多くの利点があります。

そのため、Intelは各ノード生成で複数のパスを選択できるため、興味深い選択を行うことができます。

このロードマップの時間枠を考えると、Intelはすでに10nmと7nmの次のものを決定しているかもしれません。

Intelはまた、古いが最適化されたノードでのバックポーティングについても語っています。

7nm製品は10nm +++に、5nm製品は7nm ++に、3nm製品は3nm ++に、2nm製品は3nm ++にそれぞれ移植できます。

1.4nmノードについて言及されている改良・移植はありません。

Intelが10nm ++製品(Tiger Lake)を14nm +++(Rocket Lake)にバックポーティングすることに関する最近の噂と話があります。

実質的な証拠は見つかっていますが、この製品は2021年の発売を目指しているため、Intelからこの問題について公式の言葉はありません。

しかし、このロードマップがバックポーティングについて述べていることを考えると、モビリティプラットフォームで10nm ++ノードを利用するWillow Coveコアのバックポートを備えたRocket Lake

CPUを実際に見ることができます。

解説:

Intelの製造プロセスの今後10年間の予定

Intelの製造プロセスの今後10年間の予定が出ました。

9月に行われたIEEE International Electron Devices Meetingという会合で発表されたロードマップのようです。

こちらによると今後10年間で、1.4nmに達する予定とのことです。

AMDも調子が悪かったころは製品の発表だけを行い、発売がなかなか行われない「ペーパーローンチ」を繰り返していましたが、調子の悪い半導体企業というのは行動が一種通じるものがあります。

新プロセスの発表の後に2回の改良を行う予定のようですが、要するに最初の方のプロセスは使い物にならない「可能性がある」ということです。

※ ただし、あくまでも「可能性」です。

決して順調とはいいがたい状態で進んでいるIntleの予定ですので、この通り行くとは限りません。

しかし、Intelが業界に占める地位やそれに伴う責任を考えるときちんと実行できなければ、淘汰されると考えて差し支えないと思います。

最近はIntelも危ないんじゃないかと感じるようになってきました。