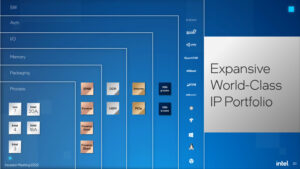

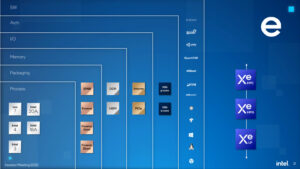

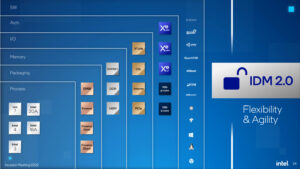

グラフィックス・アップデートに加え、インテルはCoreおよびXeonチップを含む新しいクライアントおよびサーバーCPUロードマップを発表しました。

Intelクライアント「Core」およびサーバー「Xeon」CPUロードマップを発表。2022年後半に5nm製造、2023年後半に3nm製造、2024年前半に20A、2024年後半に18A製造

インテルは、クライアントおよびサーバー部門で今後発売される製品のロードマップとマイルストーンを発表しました。

Intelは、2025年までに1ワットあたりの性能をトップに返り咲く勢いであり、この野心的な目標の達成に貢献するさまざまな製品を示していると述べている。

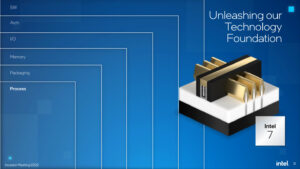

インテルは、2025年までに1ワットあたりのトランジスタ性能でトップの座を奪還する勢いを保っています。インテルの先進的なテストおよびパッケージング技術は、同社の製品やファウンドリの顧客に利益をもたらし、ムーアの法則を追求する上で重要な役割を果たす、比類ない業界リーダーシップを発揮しています」。継続的なイノベーションはムーアの法則の基礎であり、イノベーションはインテルに生きている。

インテルより

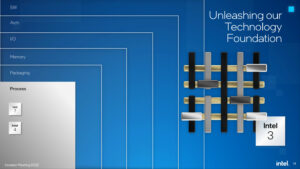

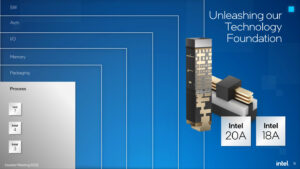

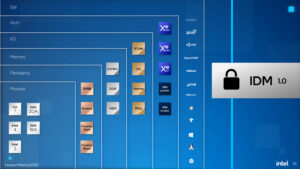

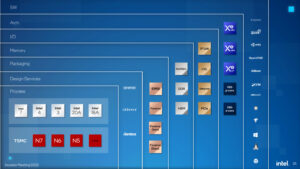

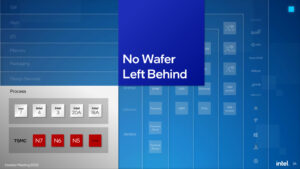

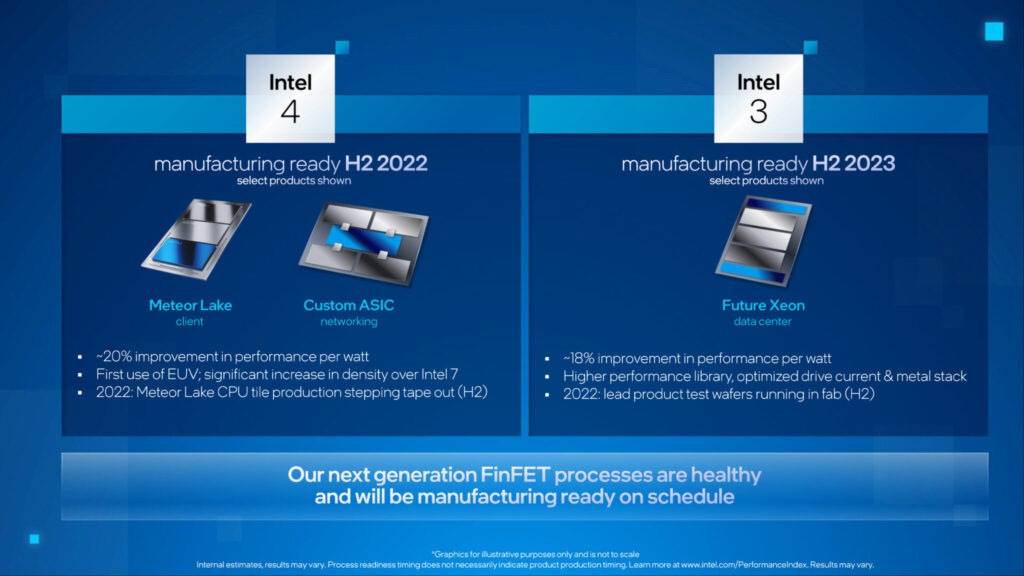

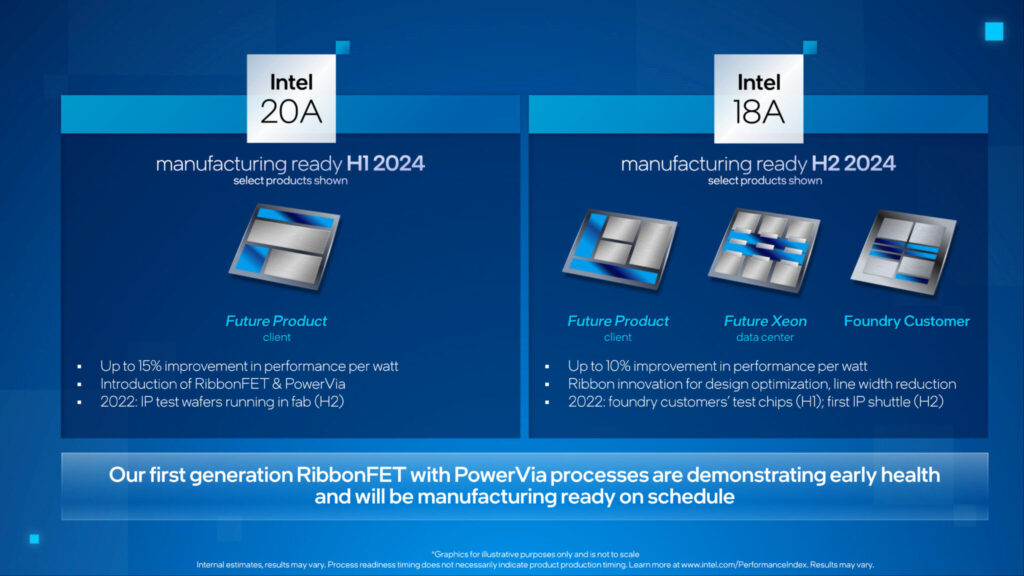

プロセス - Intel7 は、第 12 世代Intel Core プロセッサーの発売と 2022 年の追加製品に伴い量産出荷されています。Intel4は、EUV(Extreme Ultraviolet)リソグラフィーを導入したもので、2022年後半に製造可能となる予定です。これにより、1ワットあたりのトランジスタ性能が約20%向上します。Intel3は、さらに機能を追加し、1ワットあたりの性能を18%向上させ、2023年後半に製造可能な状態にする予定です。RibbonFETとPowerViaでオングストローム時代の到来を告げるIntel20Aは、1ワットあたりの性能を最大15%向上させ、2024年前半に製造可能となる予定です。Intel18Aは、さらに10%の性能向上を実現し、2024年後半に製造が開始される予定です。

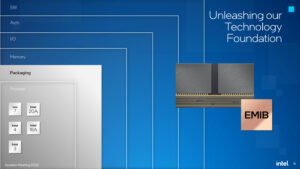

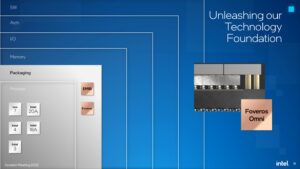

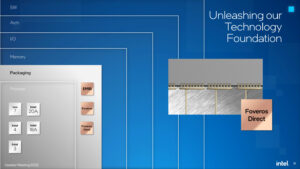

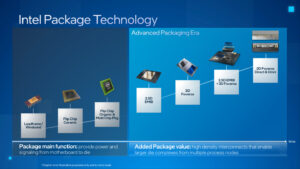

パッケージング - 当社の先進的なパッケージング・リーダーシップにより、設計者は熱、電力、高速信号、相互接続密度にわたってオプションを選択し、製品性能を最大化および協調的に最適化することができます。2022年、IntelはSapphire RapidsとPonte Vecchioのリーダーシップ・パッケージング・テクノロジーを出荷し、Meteor Lakeのリスク生産を開始する予定です。2021年7月のIntel Acceleratedで発表した先進のパッケージング技術であるFoveros OmniとFoveros Directは、2023年に製造可能な状態になる予定です。

イノベーション - Intelは、High-NA EUV、RibbonFET、PowerVia、Foveros OmniおよびDirectなどの技術に期待しており、同社のリーダーは、イノベーションに終わりはなく、したがってムーアの法則にも終わりはないと考えています。Intelは、10年後までに1つのデバイスに約1兆個のトランジスタを搭載するという目標を達成するために、決して躊躇することはありません。

※ 画像をクリックすると、別Window・タブで拡大します。

Intelプロセスロードマップ

| プロセス名 | Intel 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

| 状況 | 最多量産 (現在) | 量産 (現在) | 2022後半 | 2023後半 | 2024後半 | 2025後半 |

| ワット当りの性能 (10nm ESF超) | N/A | 10-15% | 20% | 18% | >20%? | 未確認 |

| EUV | N/A | N/A | Yes | Yes | Yes | High-NA EUV |

| トランジスタ アーキテクチャー | FinFET | 最適化された FinFET | 最適化された FinFET | 最適化された FinFET | RibbonFET | 最適化された RibbonFET |

| 製造製品 | Tiger Lake | Alder Lake Sapphire Rapids Xe-HPG? | Meteor Lake Granite Rapids Xe-HPC / Xe-HP? | Lunar Lake? Diamond Rapids? 未確認 | 未確認 未確認 未確認 | 未確認 未確認 未確認 |

Intel クライアントCPUロードマップ

IntelクライアントCPUのロードマップを始め、同社は既にAlder Lake CPUラインナップを発売しており、その後続となる第13世代Raptor Lakeラインナップを今年後半に発売予定としています。

クライアントCPUロードマップの次のアップデートは、2022年後半に「Intel 4」プロセスノードで製造され、2023年の発売が予定されている「Meteor Lake」となる予定だ。

また、Intelは2024年にMeteor Lakeに続くArrow Lakeと呼ばれる製品を投入する予定だ。Intel 4」ノードでは、ワット当たり20%の性能向上を実現し、EUV技術を初めて採用し、「Intel 7」(10nm ESF)よりも密度を大幅に向上させる予定です。

2024年以降、IntelはLunar LakeとNova LakeチップでClientプラットフォームの大規模なオーバーホールを提供する予定です。

これらは、それぞれ2025年と2026年のリリースに予定されているようです。

次世代CPUは、Tiled-CPUアーキテクチャで、MCM CPUとSOC、GPU IPを同一パッケージに統合したものになる。Lunar Lake CPUは、20Aノードを利用し、RibbonFET & Power Via技術を利用しながら、1Wあたりの性能を15%向上させる見込みです。

Nova Lakeのチップは、改良された18Aノードを利用し、1ワットあたりの性能をさらに10%向上させ、RibbonFETアーキテクチャにさらなる機能強化を図る予定です。

製造は、20Aチップが2024年前半、18Aチップが2024年後半に予定されています。

※ 画像をクリックすると、別Window・タブで拡大します。

2024年以降、IntelはLunar LakeとNova LakeチップでClientプラットフォームの大規模なオーバーホールを提供する予定です。

これらは、それぞれ2025年と2026年のリリースに予定されているようです。

次世代CPUは、Tiled-CPUアーキテクチャで、MCM CPUとSOC、GPU IPを同一パッケージに統合したものになる。

Lunar Lake CPUは、20Aノードを利用し、RibbonFET & Power Via技術を利用しながら、1Wあたりの性能を15%向上させる見込みです。

Nova Lakeのチップは、改良された18Aノードを利用し、1ワットあたりの性能をさらに10%向上させ、RibbonFETアーキテクチャにさらなる機能強化を図る予定です。

製造は、20Aチップが2024年前半、18Aチップが2024年後半に予定されています。

※ 画像をクリックすると、別Window・タブで拡大します。

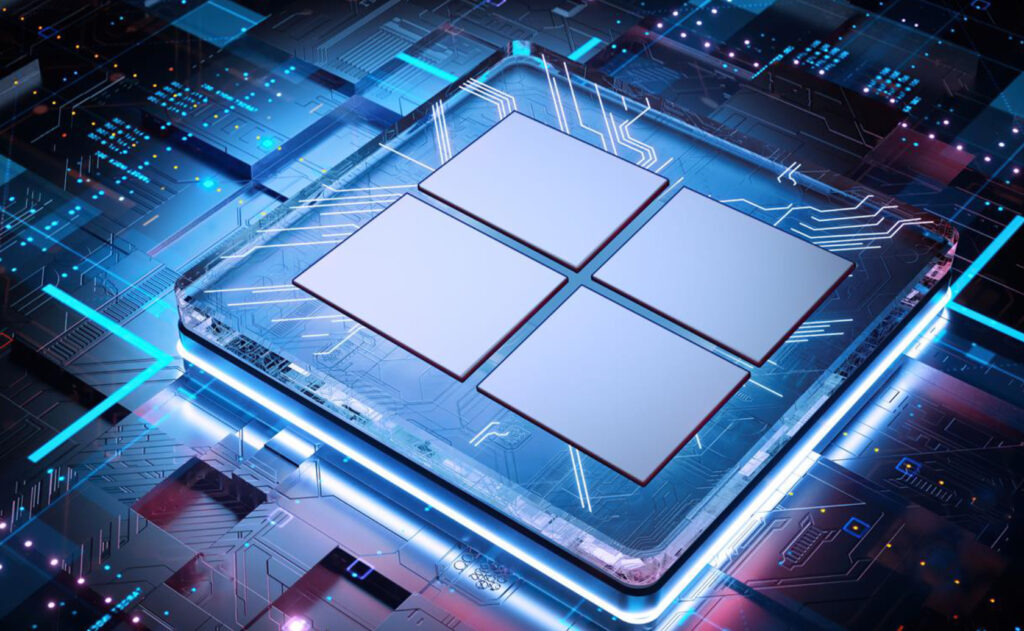

ロードマップのブロック図からわかるように、次世代クライアントプラットフォームは、同じCPUパッケージに統合される複数のチップレットを利用した、完全統合型MCM設計を採用する予定です。

全体として、チームブルーの将来のクライアントチップに期待できるチップレット数は、次のようにノード別になっている:

- 4 - 3 Chiplet SOC

- 20A - 4 Chiplet SOC

- 18A - 5 Chiplet SOC

IntelメインストリームデスクトップCPUの世代間比較:

| Intel CPU ファミリ | 製造 プロセス | 最大 コア数 | TDP | チップセット | プラット フォーム | メモリ サポート | PCIe サポート | 発売 |

| Sandy Bridge (2nd Gen) | 32nm | 4/8 | 35-95W | 6-Series | LGA 1155 | DDR3 | PCIe Gen 2.0 | 2011 |

| Ivy Bridge (3rd Gen) | 22nm | 4/8 | 35-77W | 7-Series | LGA 1155 | DDR3 | PCIe Gen 3.0 | 2012 |

| Haswell (4th Gen) | 22nm | 4/8 | 35-84W | 8-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2013-2014 |

| Broadwell (5th Gen) | 14nm | 4/8 | 65-65W | 9-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2015 |

| Skylake (6th Gen) | 14nm | 4/8 | 35-91W | 100-Series | LGA 1151 | DDR4/DDR3L | PCIe Gen 3.0 | 2015 |

| Kaby Lake (7th Gen) | 14nm | 4/8 | 35-91W | 200-Series | LGA 1151 | DDR4/DDR3L | PCIe Gen 3.0 | 2017 |

| Coffee Lake (8th Gen) | 14nm | 6/12 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Coffee Lake (9th Gen) | 14nm | 8/16 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2018 |

| Comet Lake (10th Gen) | 14nm | 10/20 | 35-125W | 400-Series | LGA 1200 | DDR4 | PCIe Gen 3.0 | 2020 |

| Rocket Lake (11th Gen) | 14nm | 8/16 | 35-125W | 500-Series | LGA 1200 | DDR4 | PCIe Gen 4.0 | 2021 |

| Alder Lake (12th Gen) | Intel 7 | 16/24 | 35-125W | 600-Series | LGA 1700 | DDR5 | PCIe Gen 5.0 | 2021Q4 |

| Raptor Lake (13th Gen) | Intel 7 | 24/32 | 35-125W | 700-Series | LGA 1700 | DDR5 | PCIe Gen 5.0 | 2022 |

| Meteor Lake (14th Gen) | Intel 4 | 未確認 | 35-125W | 800-Series? | LGA 1700 | DDR5 | PCIe Gen 5.0 | 2023 |

| Arrow Lake (15 th Gen) | Intel 4? | 40/48 | 未確認 | 900-Series? | 未確認 | DDR5 | PCIe Gen 5.0? | 2024 |

| Lunar Lake (16 th Gen) | Intel 3? | 未確認 | 未確認 | 1000-Series? | 未確認 | DDR5 | PCIe Gen 5.0? | 2025 |

| Nova Lake (17 th Gen) | Intel 3? | 未確認 | 未確認 | 2000-Series? | 未確認 | DDR5? | PCIe Gen 6.0? | 2026 |

IntelサーバーCPUロードマップ

サーバー向けには、Intelは「Intel 3」プロセスノードを利用するDiamond Rapidsという形で、最初の大きなアーキテクチャのアップリフトを提供する予定です。

このノードでは、1ワットあたりの性能が18%向上し、より高性能なライブラリ、最適化されたドライブ電流、メタルスタックを利用する予定です。

Intelは、2022年後半までに、自社ラボで主力製品(Xeon)のESTウェハーを稼働させるとしている。

また、インテルは、データセンターセグメント向けの次世代18A搭載Xeon CPUのファーストルックを初めて公開しました。

このチップは、少なくとも17個のタイルブロックを持つことが示されており、そのうち6個がCPUブロックとなっている。

※ 画像をクリックすると、別Window・タブで拡大します。

また、インテルは、データセンターセグメント向けの次世代18A搭載Xeon CPUのファーストルックを初めて公開しました。

このチップは、少なくとも17個のタイルブロックを持つことが示されており、そのうち6個がCPUブロックとなっている。

※ 画像をクリックすると、別Window・タブで拡大します。

現在のSapphire Rapids-SP Xeon CPUは、CPUタイルあたり15コアを備えているので、同じコア数の18Aチップは最大90コアを提供することになる。

ただし、2025年までには、インテルがCPUタイルあたりのコア数を増やすので、サーバーセグメントでAMDが提供する高コア数と同じ100コア以上を期待できる。

3'ノードのDiamond Rapidsは、最大144コア、288スレッドを提供する予定なので、18Aは間違いなくもっと高いコア数を提供することになる。

※ 画像をクリックすると、別Window・タブで拡大します。

Intel Xeon SP ファミリ:

| ファミリー ブランド | Skylake-SP | Cascade Lake-SP/AP | Cooper Lake-SP | Ice Lake-SP | Sapphire Rapids | Emerald Rapids | Granite Rapids | Diamond Rapids |

| 製造プロセス | 14nm+ | 14nm++ | 14nm++ | 10nm+ | Intel 7 | Intel 7 | Intel 4 | Intel 3? |

| プラット フォーム | Intel Purley | Intel Purley | Intel Cedar Island | Intel Whitley | Intel Eagle Stream | Intel Eagle Stream | Intel Mountain Stream Intel Birch Stream | Intel Mountain Stream Intel Birch Stream |

| コア アーキテクチャー | Skylake | Cascade Lake | Cascade Lake | Sunny Cove | Golden Cove | Raptor Cove | Redwood Cove? | Lion Cove? |

| IPC向上率 (前世代比) | 10% | 0% | 0% | 20% | 19% | 8%? | 35%? | 39%? |

| MCP (マルチチップ パケージ) SKUs | No | Yes | No | No | Yes | Yes | 不明(可能性 はあり) | 不明(可能性 はあり) |

| ソケット | LGA 3647 | LGA 3647 | LGA 4189 | LGA 4189 | LGA 4677 | LGA 4677 | 不明 | 不明 |

| 最大コア数 | 28 | 28 | 28 | 40 | 56 | 64? | 120? | 144? |

| 最大スレッド数 | 56 | 56 | 56 | 80 | 112 | 128? | 240? | 288? |

| 最大L3キャッシュ | 38.5 MB | 38.5 MB | 38.5 MB | 60 MB | 105 MB | 120 MB? | 240 MB? | 288 MB? |

| ベクター エンジン | AVX-512/ FMA2 | AVX-512/ FMA2 | AVX-512/ FMA2 | AVX-512/ FMA2 | AVX-512/ FMA2 | AVX-512/ FMA2 | AVX-1024/ FMA3? | AVX-1024/ FMA3? |

| サポートメモリ | DDR4-2666 6-Channel | DDR4-2933 6-Channel DDR4 2933 12-Channel | 最大6-Channel DDR4-3200 | 最大8-Channel DDR4-3200 | 最大8-Channel DDR5-4800 | 最大8-Channel DDR5-5600? | 最大12-Channel DDR5-6400? | 最大12-Channel DDR6-7200? |

| サポートされる PCIe 世代 | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 4.0 (64 Lanes) | PCIe 5.0 (80 lanes) | PCIe 5.0 (80 Lanes) | PCIe 6.0 (128 Lanes)? | PCIe 6.0 (128 Lanes)? |

| TDP範囲 | 140W-205W | 165W-205W | 150W-250W | 105-270W | Up To 350W | Up To 375W? | Up To 400W? | Up To 425W? |

| 3D Xpoint Optane DIMM | N/A | Apache Pass | Barlow Pass | Barlow Pass | Crow Pass | Crow Pass? | Donahue Pass? | Donahue Pass? |

| 競合 | AMD EPYC Naples 14nm | AMD EPYC Rome 7nm | AMD EPYC Rome 7nm | AMD EPYC Milan 7nm+ | AMD EPYC Genoa ~5nm | AMD Next-Gen EPYC (Genoa後継) | AMD Next-Gen EPYC (Genoa後継) | AMD Next-Gen EPYC (Genoa後継) |

| 発売 | 2017 | 2018 | 2020 | 2021 | 2022 | 2023? | 2024? | 2025? |

解説:

Intelのロードマップが更新されたようですのでそれが記事になっています。

タイトルを見たらMeteorLakeが遅れると思ったのですが、よく見ると予定通りだったので、単に情報が更新されたということのようですね。

とてもわかりづらくなったIntelの製造プロセス

私はIntelとTSMCの製造プロセスの関係をトランジスタ密度で理解していたのですが、Intelが表記の基準をTSMCの製造プロセスのどれに相当するか?に変更したため、かえってわかりにくくなってしまいました。

自分への備忘録として元記事の表に旧プロセスネームを追加したものを置いておきます。

| プロセス名 | Intel 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

| 状況 | 最多量産 (現在) | 量産 (現在) | 2022後半 | 2023後半 | 2024後半 | 2025後半 |

| 旧来表記による 製造 プロセス | 10nm | 10nm | 7nm | 7nm | 5nm | 5nm |

| ワット当りの性能 (10nm ESF超) | N/A | 10-15% | 20% | 18% | >20%? | 未確認 |

| EUV | N/A | N/A | Yes | Yes | Yes | High-NA EUV |

| トランジスタ アーキテクチャー | FinFET | 最適化された FinFET | 最適化された FinFET | 最適化された FinFET | RibbonFET | 最適化された RibbonFET |

| 製造製品 | Tiger Lake | Alder Lake Sapphire Rapids Xe-HPG? | Meteor Lake Granite Rapids Xe-HPC / Xe-HP? | Lunar Lake? Diamond Rapids? 未確認 | 未確認 未確認 未確認 | 未確認 未確認 未確認 |

3nmから先は未定だったはずですので、これであっていると思います。

Intelは製造プロセスの微細化+トランジスタのアーキテクチャーの改良を組み合わせてTSMC基準で表記するように変更したようです。

最初はどうかと思いましたが、製造プロセスのトラブル続きでしたので、マーケティング上、トランジスタのアーキテクチャーと言う新しい項目を加えてリブランドしたのは成功だったと思います。

ただし、あくまでも結果論です。

Intelでは、製造プロセスとトランジスタ・アーキテクチャーの改良により、10-20%の効率改善が見られれば「成功」として次のプロセスネームを与えるというルールに変更したようです。

スケジュールが守れるのならば現実的で顧客からの信頼も回復し、良い方法だと思います。

微細化が進まなければ「失敗」とするのはもう現実的ではないということになります。

TSMCは3nmが遅れるかもしれないという話が出ていますが、積層型も含めトランジスタのアーキテクチャーの改良はIntelに後れを取っているように見えます。

私がこう思っている時点で、Intelの製造プロセスのリブランドは大成功していると言ってもよいのではないでしょうか(苦笑。

あとは、TSMCが3nm、2nmをどのようなスケジュールで出してくるかによって、決まってくると思います。

さすがに、TSMCのプロセスに全く敵わないということは無いと思いますが・・・・。

Core Ultra 200Sシリーズ

ソケットLGA1851

※ 末尾にFがついているモデルはGPUがありませんのでご注意ください。