IBMは本日、世界初の2nmプロセスと称する「2nm」プロセス技術を発表しました。

プロセスの命名法は、世の中の様々なファッションスタイルのように、急速に標準化されつつあります。

ほぼすべてのメーカーが独自にノードの定義を持っており、中にはより寛大なものもあります。

IBMは、ナノシート技術を用いて持続的なプロセス改善を達成した最初の企業であると思われますが、これは2nmの主張よりもはるかにエキサイティングなことです。

IBM、ナノシート技術で2nmプロセスを実現

一般的に、プロセスの微細化は、同じダイ面積で50%の改善をもたらします。

そのため、企業がFinFETのようなエキゾチックな技術を採用し始め、実際にダイサイズを小さくすることなく同じ改善を得られるようになると、ノードサイズの「真の」価値から遠ざかってしまいます。

明確に言うと、現在、どのメーカーも正直にノードの命名をしているわけではありませんが、その厳しさでランク付けすると、Intelの命名はTSMCなどの約2倍の厳しさです。

例えば、Intelの7nmプロセスは、TSMCの5nmプロセスとほぼ同じです。

TSMCの5nmプロセスは、50%の改善にもなっていません(7nmに対して15%の改善しかありません)。

IBMの主張によれば、彼らの「2nm」技術はTSMCの7nmに比べて約50%の改善を実現しており、今日の最も寛大な基準でもせいぜい3.5nm技術になるという。

話は変わりますが、彼らのメッセージには驚くべきことが隠されています。

リソグラフィーがますます複雑化している世界では、次のFinFETや縮小を続ける製造技術を見つけるための競争が行われています。

高NAのEUVもその一つですが、IBMはナノシート技術でもう一つのものを見つけ出したようです。

マニアの私にとって、これは信じられないほどエキサイティングなニュースで、2nmのマーケティングメッセージをはるかに上回るものです。TSMCの最小ピッチサイズは30nmで、IBMが20nm以下になるとは思っていません。

また、量子トンネル現象(ゲートがゲートとして機能しなくなり、電子が単にトランジスタを通過するようになる)やビット反転現象(トランジスタがますます小さくなると、宇宙線の影響でトランジスタが反転し、500のトランザクションが500万になってしまうなど)の問題をどのように解決するのか、興味深いところです。

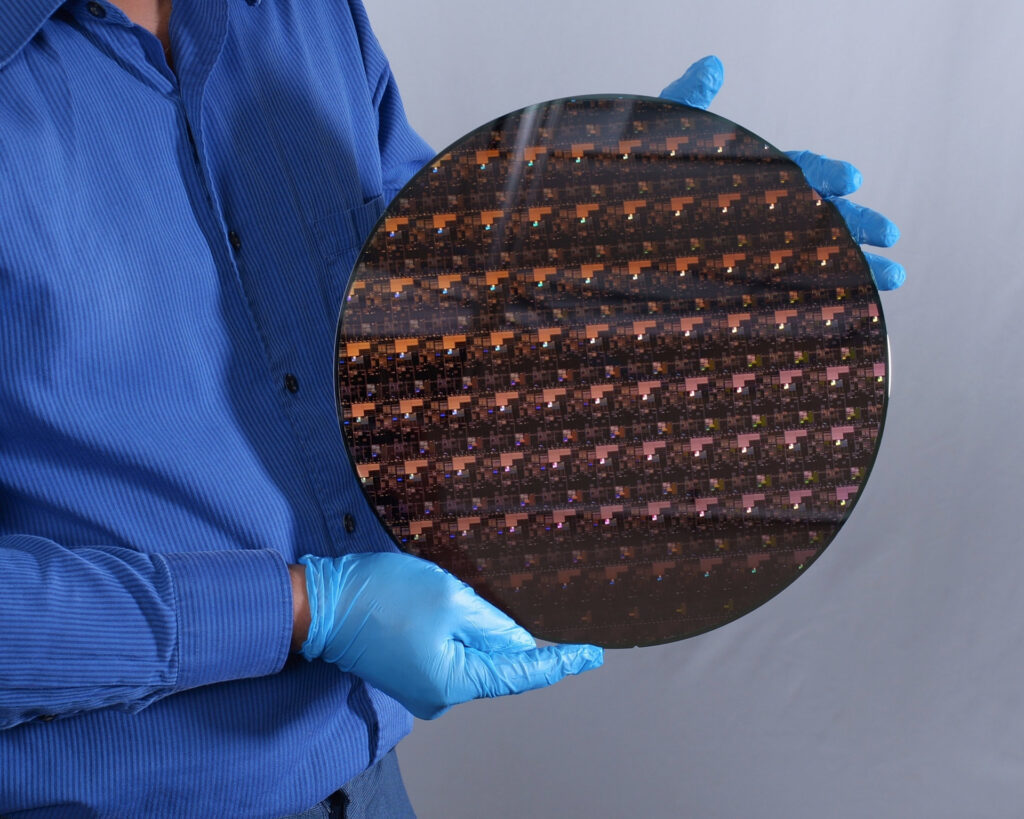

ニューヨーク州アルバニー、2021年5月6日 - IBM(NYSE: IBM)は本日、2ナノメートル(nm)のナノシート技術を用いて発表した世界初のチップを開発し、半導体の設計とプロセスにおける画期的な技術を発表しました。

半導体は、コンピュータ、家電、通信機器、交通システム、重要なインフラなど、あらゆるものに重要な役割を果たしています。

特にハイブリッド・クラウド、AI、モノのインターネットの時代には、チップの性能向上とエネルギー効率の向上に対する需要が高まり続けています。

IBMの新しい2nmチップ技術は、このような需要の高まりに対応し、半導体業界の最先端を前進させるものです。現在の最先端である7nmノードのチップシと比較して、45%の性能向上、または75%のエネルギー使用量削減を実現すると予測されています。

この先進的な2nmチップの潜在的なメリットとしては、以下のようなものが考えられます。

- 携帯電話のバッテリー寿命が4倍になり、ユーザーは4日に1回の充電で済むようになる

- 世界のエネルギー使用量の1%を占めるデータセンターの二酸化炭素排出量を削減することができる。すべてのサーバーを2nmベースのプロセッサーに変更することで、この数字を大幅に削減できる可能性があります。

- アプリケーションの処理速度の向上、言語翻訳の容易化、インターネットの高速化など、ノートPCの機能を大幅に向上させる。

- 自動運転車のような自律走行車の物体検出や反応速度の高速化に貢献する。

"この新しい2nmチップに反映されているIBMのイノベーションは、半導体およびIT業界全体にとって必要不可欠なものです。」と、IBMリサーチのSVP兼ディレクターであるダリオ・ギルは述べています。

"これは、困難な技術的課題に挑戦するIBMのアプローチの産物であり、持続的な投資と協力的なR&Dエコシステムのアプローチからいかにブレークスルーがもたらされるかを示すものです。"

半導体技術革新の最前線に立つIBM

この最新のブレークスルーは、半導体革新におけるIBMの数十年にわたるリーダーシップに基づくものです。

IBMの半導体開発は、ニューヨーク州アルバニーのアルバニー・ナノテック・コンプレックスにある研究所を拠点としており、IBMの科学者たちは、官民のパートナーと密接に協力しながら、論理のスケーリングと半導体の能力の限界を押し広げています。

このようなイノベーションへの協力的なアプローチにより、IBMリサーチ・アルバニーは、半導体研究における世界有数のエコシステムとなり、強力なイノベーション・パイプラインを構築して、製造需要に対応し、世界のチップ産業の成長を加速しています。

IBMは、7nmおよび5nmプロセス技術、シングルセルDRAM、Dennard Scaling Laws、化学増幅型フォトレジスト、銅配線、Silicon on Insulator技術、マルチコアマイクロプロセッサ、High-kゲート絶縁膜、エンベデッドDRAM、3Dチップスタッキングなど、半導体のブレークスルーを実現してきました。

IBM研究の7nmの進歩を含むIBMの最初の商品化された製品は、今年の後半にIBM POWER10ベースのIBM Power Systemsでデビューする予定です。

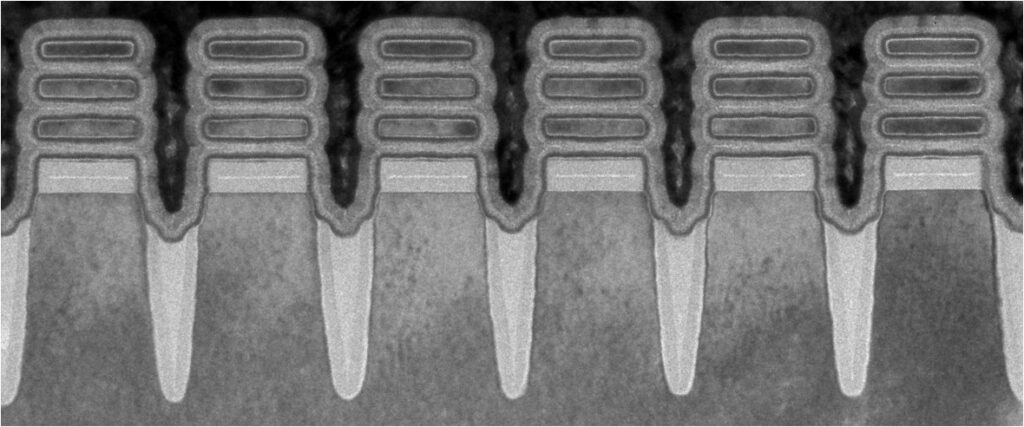

指の爪サイズのチップに500億個のトランジスタを搭載

チップあたりのトランジスタ数を増やすことで、チップの小型化、高速化、信頼性の向上、効率化を図ることができます。

2nmのデザインは、IBMのナノシート技術を用いた半導体の高度なスケーリングを実証しています。

そのアーキテクチャは業界初のものです。IBMがマイルストーンとなる5nm設計を発表してから4年も経たないうちに開発されたこの最新のブレークスルーにより、2nmチップでは指の爪ほどの大きさのチップに最大500億個のトランジスタを搭載することができます。

チップ上のトランジスタ数が増えるということは、プロセッサー設計者にとって、AIやクラウドコンピューティングなどの最先端のワークロードに対応する機能を向上させるコアレベルのイノベーションを注入するための選択肢が増えることを意味し、また、ハードウェアで強化されたセキュリティや暗号化のための新たな経路を提供します。

IBMはすでに、IBM POWER10やIBM z15などの最新世代のIBMハードウェアに、他の革新的なコアレベルの機能強化を実装しています。

解説:

IBMが世界初の2nm製造プロセスを発表

| ゲートピッチ (nm) | トランジスタ密度 (MTr/mm2) | |

| IBM | ||

| 2nm | 20-30 | 不明 |

| TSMC | ||

| 16/12nm | 88 | 28.88 |

| 10nm | 64 | 51.51 |

| 7nm | 54 | 96.5 |

| 7nmP | 54 | 96.5 |

| 7nm+ | 不明 | 113.9 |

| 6nm | 不明 | 114.2 |

| 5nm | 44 | 185.46 |

| 3nm* | 39 | 315.28 |

| 2nm* | 30 | 333.83 |

| Intel | ||

| 14nm | 70 | 37.5 |

| 10nm | 54 | 100.76 |

| 7nm | 不明 | 202-250 |

| Samsung | ||

| 14nm | 78 | 32.94 |

| 10nm | 68 | 51.82 |

| 8nm | 64 | 61.18 |

| 7nm | 54 | 95.3 |

上の表にゲートピッチとトランジスタ密度の比較を載せました。

現在出ていない製造プロセスは計算で出していますので誤差があると思います。

IBMの2nmはゲートピッチが20-30nmの間と言われていますので、なかなか高スペックです。

TSMCの2nmより上と言うことになります。

SamsungとTSMCのプロセス名とスペックは大体似ていますが、Intelのプロセス名とスペックは他社とは違うので要注意です。

同一のプロセスでも複数ある場合は値が一番大きいものを表記しています。

90nm時代にSOIと言う技術でAMDと組んでIntelを引き離し、第1期AMD黄金時代を築いたIBMですが、現在でも製造プロセスの技術開発は第一線のところにあるようです。

直接CPU戦争に影響を与える可能性はあまりないかもしれませんが、世界最先端レベルの製造技術であり、興味深いニュースでしたので、一応紹介しておきます。