DigiTimesの新しいレポートによると、NVIDIAはTSMCのCoWoSパッケージを使用する3つの重要なクライアントの1つになり、他の2つのクライアントはザイリンクスとHiSiliconになります。

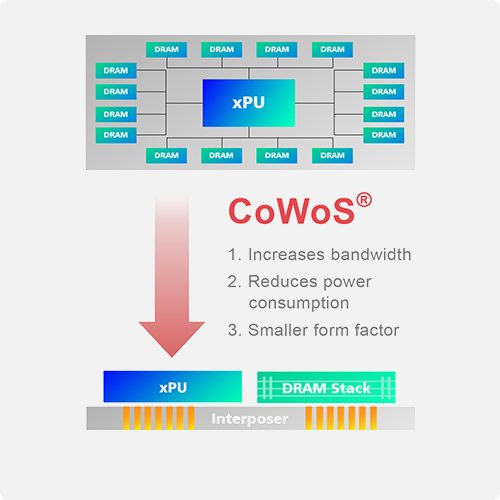

CoWoSまたはChip-on-Wafer-on-Substrateは、複数のチップレットを単一のインターポーザに統合する2.5Dパッケージング技術です。

この新しいパッケージングテクノロジには多くの利点がありますが、主な利点にはフットプリントの大幅な削減と消費電力の削減が含まれます。

NVIDIAは、次世代HPC GPUにTSMCのCoWoSテクノロジーを使用している可能性があります

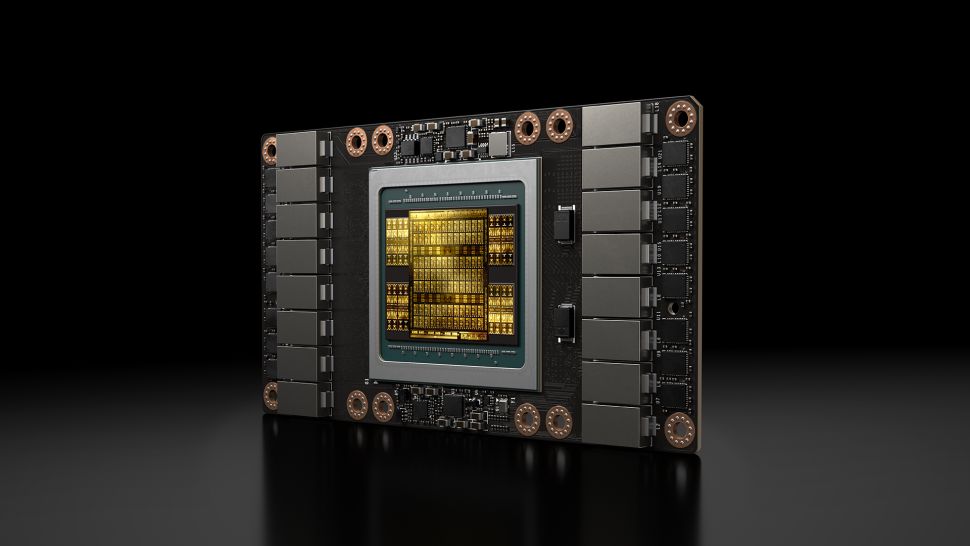

Nvidiaは過去にCoWoSパッケージを既に使用しており、この技術は多くのハイエンドTitan、Quadro、Teslaグラフィックカードに搭載されています。

この技術は、パスカル時代までさかのぼって実装されています。

GP100(Pascal)およびGV100(Volta)シリコンは、CoWoSパッケージングを利用する2つの特定の例です。

前者はファウンドリの16nm FinFET製造プロセスに基づいており、後者は12nmノードから利益を得ています。

AMDのVega20 7nmシリコンもCoWoSテクノロジーを使用してパッケージ化されていますが、DigiTimesはトップ3リストにAMDを含めていません。

これは、NVIDIA、Xilinx、およびHiSiliconがTSMCのCoWoS生産能力の大部分を獲得することを意味します。

TSMCは毎月6,000から8,000枚のウェーハを送り出すと伝えられているため、十分な量の製品が存在するはずです。

悲しいことに、NVIDIAのコンシューマグラフィックスカードにCoWoSテクノロジーが実装されることはまずありません。

これは、消費者に転嫁するコストが高いためです。

NVIDIAは、過去と同様に、CoWoSテクノロジーをQuadroおよびTeslaCoWoSテクノロジーファミリーのGPUに追加する可能性が最も高いでしょう。

Ampereは、NVIDIAの次世代GPUアーキテクチャのコードネームですが、MCMまたはマルチチップモジュールデザインを利用するという兆候はありません。

ただし、Ampereに続くGPUの現在のコード名であるHopperは、MCMテクノロジに依存している可能性があります。

ソース:wccftech - NVIDIA May Potentially Utilize TSMC’s CoWoS Packaging for the Next-Generation GPUs

解説:

TSMCの製造技術に関する話題です。

CoWoSを使うと帯域幅の増大、省電力性、ダイをより小さくできるようです。

このCoWoSテクノロジーはQuadroおよびTesla向けの製造技術ということのようですね。

基本的に価格を安くあげる必要のあるコンシュマー製品であるGeforceには使われないようです。

AMDだとRadeon Instinct. MI60, MI50あたりにも使われているようですね。

このCoWoSテクノロジーはNVIDIA、Xilinx、およびHiSiliconが生産トップ3を占めるようです。

nVidiaはともかく、Xilinx(ザイリンクス)とHiSiliconは初耳の方もいると思いますので簡単に説明しておくと、ザイリンクスはAIコアというAI処理用の製品Versalシリーズを持っており、そちらで使うのだと思います。

HiSiliconはご存知の方も多いと思いますが、こちらはHuawei製品のSoCの生産に使われます。