大量生産の2四半期前

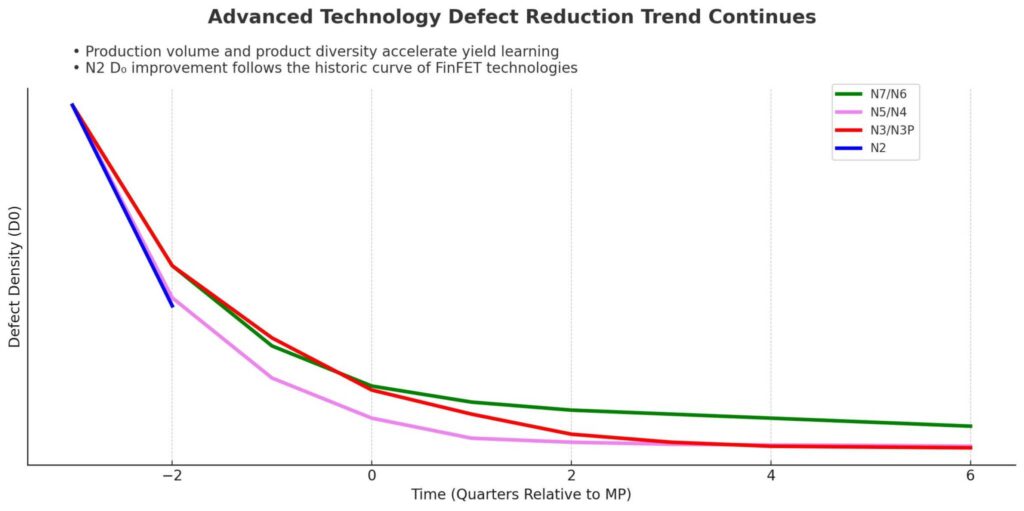

TSMCは今週開催された北米技術シンポジウムで、N2プロセス技術の欠陥密度(D0)について、同じ開発段階にある先行技術との比較で明らかにした。同社によると、欠陥密度はN3、N5、N7の製造ノードを下回っているという。また、ComputerBaseが公開したスライドによると、N2は量産まであと4分の2であり、これはTSMCが予想通り2025年第4四半期後半に2nmクラスのチップ製造を開始する予定であることを意味する。

TSMCのN2は、ゲートオールアラウンド(GAA)ナノシートトランジスタを採用した同社初のプロセス技術だが、同ノードは、量産(MP)2四半期前の同じ開発段階の先行技術よりも欠陥密度が低い。

前身のN3/N3P、N5/N4、N7/N6はいずれも、よく知られたFinFETトランジスタに依存していた。

そのため、TSMCにとってGAAナノシート・トランジスタを使用する最初のノードであるにもかかわらず、N2の欠陥密度は、量産(HVM)マイルストーン前の前技術の欠陥密度よりも早く(まあ、急峻に)低くなっている。

このグラフは、欠陥密度を時間に対してプロットしたものである。N7/N6(緑)、N5/N4(紫)、N3/N3P(赤)、N2(青)の全ノードで、欠陥密度は、ノードの複雑さによって速度は異なるものの、生産が進むにつれて大幅に減少している。

注目すべきは、N5/N4が初期の欠陥低減に最も積極的であるのに対し、N7/N6はより緩やかな歩留まり改善を示していることである。

N2カーブは、N5/N4よりも高い初期欠陥レベルで始まるが、急激に減少し、N3/N3Pの欠陥減少の軌跡と密接に一致する。

このスライドでは、欠陥密度の改善を加速させる主な原動力は、依然として生産量と製品の多様性であることが強調されている。

より多くの生産量と、同じプロセスを使用する多種多様な製品により、欠陥密度や歩留まりの問題をより迅速に特定・修正することが可能になり、TSMCは欠陥学習サイクルを最適化することができる。

TSMCは、同社のN2製造技術は、(TSMCが現在、スマートフォンやHPCの顧客向けにN2チップを製造するリスクを負っているため)前技術よりも多くの新規テープアウトを獲得したと述べており、欠陥密度の減少曲線はほぼそれを証明している。

N2の欠陥減少率が以前のFinFETベースのノードとよく一致しているという事実は、まったく新しいトランジスタ・アーキテクチャの導入に伴うリスク要因を考えると、特に重要である。

これは、TSMCがプロセス学習と欠陥管理の専門知識を、(少なくともTSMCが開示している内容に基づけば)大きな挫折をすることなく、新しいGAAFET時代にうまく移行できたことを示唆している。

ソース:Tom's Hardware - TSMC discloses N2 defect density — lower than N3 at the same stage of development

解説:

欠陥密度というのは対象システムの単位量のあたりのバグや欠陥の数のことです。

最初にグラフを見た時はTSMCの2nmは欠陥密度が高いという意味なのかと思っていましたが、急速に改善して同時期のN3より低くなっているということのようです。

さすがにTSMCは盤石なのかなと思います。

一時期TSMCはN2の進展の報告がなく、A14の話も出てきていませんでした。

Intel 18Aの方が先行していたため、2nmやポスト2nm世代ではIntel優勢になるのかなと思っていた時期もありましたが、もう全然比べ物にならないほど安定しているようですね。

Intelと比較していたころの自分を殴りたいくらいです。

やはり半導体Fab世界一の実績は伊達ではないと思います。

2nmからFinFetからGAAになりましたが、それでもプロセスの改善は順調のようです。

N3世代よりも多くの受注を取れているようで、本当に盤石という言葉以外思い浮かびません。

ここに新規で参入する日本のラビダスも頑張ってほしいところですが、TSMCと同等以上のレベルで戦うのは厳しいように思います。

今は最新技術はまずArm勢やスマホが使うようになり、PCには一周回った後に使われるようになりました。

TSMC2nmの製品を我々自作erが手にするのはもう少し後になると思いますが、その日が楽しみでなりません。