Intelファウンドリーは、トランジスタとパッケージング技術の領域における「画期的な」開発を披露し、材料とシリコンの革新を明らかにした。

Intelファウンドリー、ノードのスケーラビリティを確保する「サブトラクティブ・ルテニウム」と新トランジスタ技術を披露

[プレスリリース]: 本日、IEEE International Electron Devices Meeting(IEDM)2024にて、Intel Foundry社は、半導体業界を次の10年、そしてその先へと前進させるためのブレークスルーを発表した。

Intelファウンドリーは、チップ内の相互接続を改善するのに役立つ新材料の進歩を披露し、減法ルテニウムの使用により最大25%のキャパシタンスを実現した。

Intelファウンドリーはまた、超高速チップ・ツー・チップ・アセンブリを可能にするアドバンスト・パッケージング用のヘテロジニアス・インテグレーション・ソリューションを使用して、100倍のスループット向上を初めて報告した。

ゲート・オール・アラウンド(GAA)スケーリングをさらに推進するため、Intelファウンドリーは、シリコンRibbonFET CMOSと、デバイス性能を向上させるスケーリングされた2D FET用のゲート酸化膜モジュールとの連携を実証した。

重要な理由:業界が2030年までに1兆個のトランジスタをチップに搭載することを目指す中、トランジスタとインターコネクトのスケーリングにおけるブレークスルーは、将来の高度なパッケージング能力と相まって、AIなどのよりエネルギー効率に優れ、高性能でコスト効率の高いコンピューティング・アプリケーションに対する限りない欲求を実現するために不可欠です。

業界はまた、ムーアの法則の継続とAIのための新しい時代への半導体の推進に不可欠である、相互接続の混雑を緩和し、継続的なスケーリングのために、Intel FoundryのPowerViaバックサイドパワーデリバリを補強する新しい材料の形でさらなるサポートを必要とする。

我々はどのようにそれを行っているか:Intelファウンドリーは、将来のノードのインターコネクトのスケーリングにおける銅トランジスタの限界を解決し、 既存のアセンブリ技術を改善し、ゲートオールアラウンドのスケーリングとその先のトランジスタのロードマップを 定義し、形成し続けるためのいくつかの道を特定しました:

- サブトラクティブ・ルテニウム(Ru): チップ内の性能と相互接続を向上させるため、Intelファウンドリーは、薄膜の抵抗率とエアギャップを利用して相互接続のスケーリングを大幅に進歩させる新しい主要な代替メタライゼーション材料であるサブトラクティブ・ルテニウムを展示した。チームは、R&Dテスト車両において、ビア周辺の高価なリソグラフィによるエアギャップ排除ゾーンや、選択的エッチングを必要とするセルフアライメント・ビアフローを必要としない、実用的でコスト効率に優れ、大量生産に対応するエアギャップ付きサブトラクティブ・ルテニウム集積プロセスを初めて実証した。サブトラクティブ Ru によるエアギャップの実装は、25 ナノメートル(nm)以下のピッチでライン間キャパシタンスを最大 25%削減し、タイトピッチ層の銅ダマシン(Damascene)に代わるメタライゼーション・スキームとしてのサブトラクティブ Ru の利点を示しています。このソリューションは、Intelファウンドリーの将来のノードで見られる可能性がある。

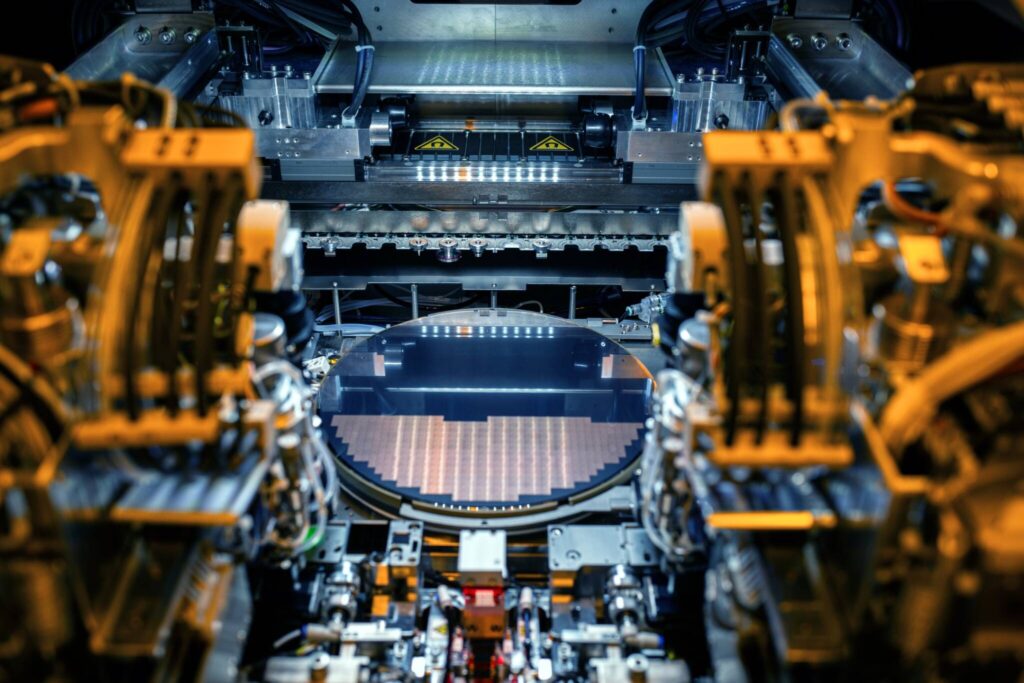

- 選択的レイヤー・トランスファー(SLT): 先端パッケージングにおける超高速チップ間アセンブリのスループットを最大100倍まで向上させるため、Intelファウンドリーは、従来のチップ間ボンディングに比べ、より小さなダイサイズと高いアスペクト比を可能にする柔軟性に優れた超薄型チップレットを実現するヘテロジニアス・インテグレーション・ソリューションであるSLT(Selective Layer Transfer)を世界で初めて実証しました。これにより、より高い機能密度が可能になり、特定のチップレットをウェーハ間でハイブリッド接合またはフュージョン接合するための、より柔軟でコスト効率の高いソリューションが実現します。このソリューションは、AIアプリケーションにより効率的で柔軟なアーキテクチャを提供します。

シリコンRibbonFET CMOS: ゲート全面RibbonFETシリコンの微細化を限界まで押し進めるため、Intelファウンドリーは、積極的に微細化されたゲート長とチャネル厚で業界をリードする短チャネル効果と性能を持つ、ゲート長6nmのシリコンRibbonFET CMOS(相補型金属酸化膜半導体)トランジスタを展示しました。この進歩は、ムーアの法則の基礎となる重要な基盤のひとつであるゲート長スケーリングの継続に道を開くものです。 - 微細化GAA 2DFET用ゲート酸化膜: CFETを超えるゲート全周イノベーションをさらに加速するため、Intel Foundryは、ゲート酸化物(GOx)モジュール開発に特に焦点を当て、ゲート長を30nmまで縮小したGAA 2D NMOSおよびPMOSトランジスタの製造に関する研究を紹介した。この研究は、2次元(2D)遷移金属ジカルコゲナイド(TMD)半導体の業界調査に関するもので、将来の先端トランジスタプロセスにおけるシリコン代替となる可能性がある。

さらに、Intelファウンドリーは、シリコンよりも高い性能と高い電圧・温度を維持できるパワーおよび無線周波数(RF)エレクトロニクス向けの新技術である、業界初の300ミリメートル(mm)窒化ガリウム(GaN)技術の研究を進めました。

これは業界初の高性能エンハンスメントモードGaN MOSHEMT(金属-酸化膜-半導体高電子移動度トランジスタ)であり、300 mmのGaN-on-TRSOI(「トラップリッチ」シリコンオンインシュレータ)基板上に作製された。

GaN-on-TRSOIのような高度に設計された基板は、RFやパワーエレクトロニクスのようなアプリケーションにおいて、信号損失を低減し、より優れた信号直線性を実現することで、より優れた性能を達成することができる。

IEDM 2024の詳細: 会議では、Intel Foundryが、AIを含むアプリケーション全体の需要に対応するための高度なパッケージングとトランジスタのスケーリングの将来についてのビジョンも発表した。より電力効率の高いAIに向けた次の10年を推進するため、技術革新の3つの重要な柱が特定された。

- 容量、帯域幅、レイテンシのボトルネックを解消する高度なメモリ統合。

- ハイブリッドボンディングによるインターコネクト帯域幅の最適化

- 対応するコネクティビティ・ソリューションによるモジュラー・システム拡張。

Intelファウンドリーはまた、1兆トランジスタ時代に向けてトランジスタのスケーリングを継続するために、重要かつ画期的なイノベーションを開発するよう呼びかけた、Intel ファウンドリーは、超低電圧動作(300ミリボルト未満)が可能なトランジスタを開発することで、増大する熱ボトルネックに対処し、エネルギー消費と熱放散を劇的に改善できることを説明した。

解説:

Intelファウンドリーからトランジスタとパッケージング技術の「革新的」戦略が発表されましたので取り上げてみました。

数々の新しい技術が発表されています。

新技術といえばDLVRが記憶にあたらしいですが、デスクトップではうまく活用されませんでしたので、デスクトップユーザーにすべての技術が有効とは限らないです。

近年ではモバイルの方が出荷数が圧倒的に多いですから、なおのことですね。

こうした動きは先日の歩留まりの問題が明るみに出た対策なのでしょうか。

私はIntelのFabの存続は現時点では怪しいと思いますが、別にIntel自体が倒産するとは思ってません。

IntelのFabは昨年度の決算で1.5兆円も赤字を垂れ流していますから、今の状態での存続は厳しいと思います。

先日の歩留まりの報道で完全に赤信号がともっていると思います。

それでも今の難局を乗り切れれば何とかなる可能性が0ではないのでしょうね。

この記事を見るとそう思います。

ただ、営利企業というのは期間を区切った業績で評価されるものであること、競争相手がTSMCであることを考えるとなかなか厳しい道のりが待っていると言わざるを得ません。

Core Ultra 200Sシリーズ

ソケットLGA1851

※ 末尾にFがついているモデルはGPUがありませんのでご注意ください。