Zen 5コアを搭載するAMDのEPYC Turin CPUの後継は、EPYC Veniceと呼ばれ、Zen 6アーキテクチャを搭載すると噂されていると、Moore's Law is Deadが報じています。

AMD EPYC Venice サーバーCPUは、200以上のZen 6コアを搭載し、L2/L3キャッシュとHBM SKUを再設計したとの噂

この製品が2025年以上まで発売されないことを考えると、現時点では詳細はかなり曖昧ですが、MLIDはコードネームに関する非常に初期の詳細を入手したようで、AMDのマーケティングは次世代EPYCラインアップのために「Venice」を思いついたようです。

イタリア北東部のヴェネト州の州都にちなんで名付けられたEPYC Veniceのラインナップは、サーバーにとって大きなアップデートとなることが期待されています。

レッドチームが2025年以降もZenネーミングを継続するのか、それとも別のものに移行するのかは不明だが、共有されているいくつかの詳細には、AMD Zen 6コアへの言及が含まれている。

サーバーセグメントでは、EPYCの命名規則が継続される。

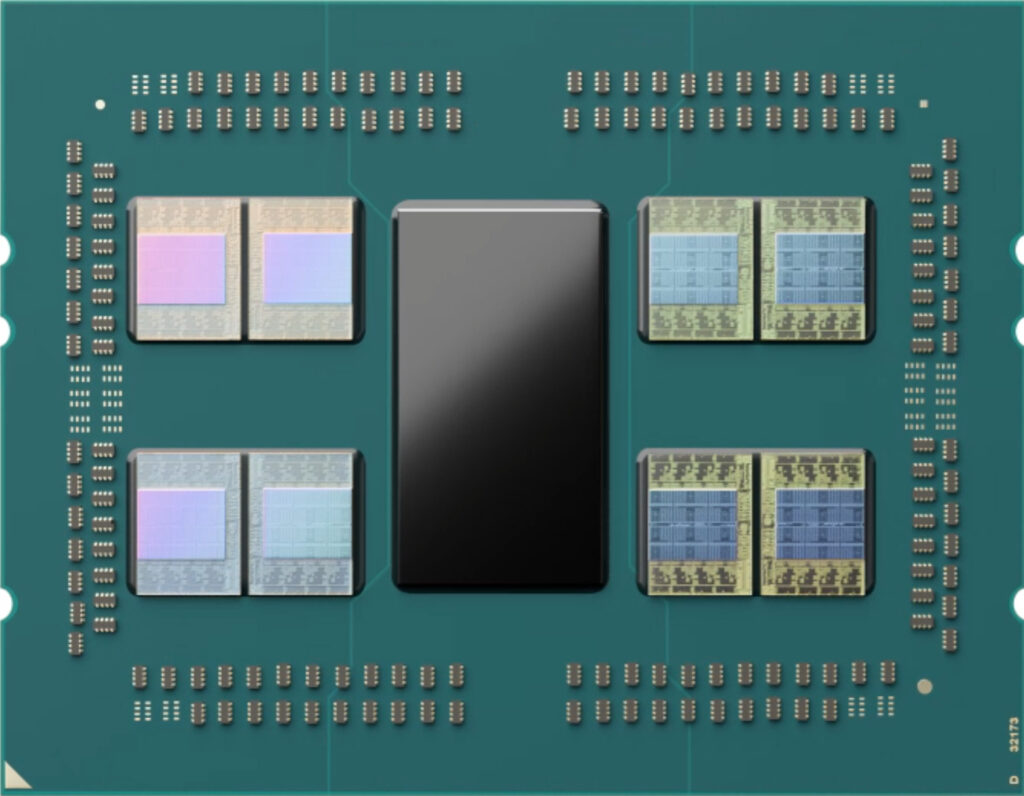

Zen 6、あるいはZen 5以降のx86アーキテクチャは、非常にハイブリッドなコア設計手法を用いると言われており、200コア以上(控えめに見積もって)を提供できるとされており、ソケットあたり最大384コアの噂がある。

このCPUがSP5プラットフォームと互換性があるかどうかは言及されていないが、Turinとそれに続くZen 5Cが、次期プラットフォーム向けの最後のEPYCチップになる可能性があるようだ。

SP5ソケットは2025年まで続くので、アップデートを提供するには良い期間だと思います。

また、アーキテクチャ自体のアップグレードについては、AMDがL2キャッシュとL3キャッシュのシステムを完全に再設計する見込みであることをリーク元は述べている。

Infinity Cacheアーキテクチャも大きな変化を遂げるだろう。

また、HBMはほとんどのラインナップで標準となり、次世代EPYC CPUでは、このメモリ規格が大きな役割を果たすことになる。

EPYCに統合されたオンボードのHBMハイブリッド設計は、同じコア数の中でIPCを拡張するために利用することができる。

また、EPYC Veniceが複数のSKUでHBMを標準化する一方で、Zen 5ベースのEPYC製品がHBM設計を採用した最初のAMD EPYCサーバー製品の1つになるとTomは予想しています。

結局のところ、これらすべてが素晴らしく聞こえますが、私たちは今から3~4年後に発売される製品について話しており、その間に多くのことが変わり得ることを忘れてはいけません。

しかし、AMDのEPYC Veniceは本当に実現しそうで、数年後に実際に動く姿を見るのが待ち遠しいですね。

AMD EPYC CPU ファミリ:

| ファミリー ネーム | AMD EPYC Naples | AMD EPYC Rome | AMD EPYC Milan | AMD EPYC Milan-X | AMD EPYC Genoa | AMD EPYC Bergamo | AMD EPYC Turin |

| ファミリー ブランド | EPYC 7001 | EPYC 7002 | EPYC 7003 | EPYC 7003X? | EPYC 7004? | EPYC 7005? | EPYC 7006? |

| 発売時期 | 2017 | 2019 | 2021 | 2022 | 2022 | 2023 | 2024-2025? |

| CPU アーキテクチャー | Zen 1 | Zen 2 | Zen 3 | Zen 3 | Zen 4 | Zen 4C | Zen 5 |

| 製造プロセス | 14nm GloFo | 7nm TSMC | 7nm TSMC | 7nm TSMC | 5nm TSMC | 5nm TSMC | 3nm TSMC? |

| プラットフォーム | SP3 | SP3 | SP3 | SP3 | SP5 | SP5 | SP5 |

| ソケット | LGA 4094 | LGA 4094 | LGA 4094 | LGA 4094 | LGA 6096 | LGA 6096 | LGA 6096 |

| 最大コア数 | 32 | 64 | 64 | 64 | 96 | 128 | 256 |

| 最大スレッド数 | 64 | 128 | 128 | 128 | 192 | 256 | 512 |

| 最大L3キャッシュ | 64 MB | 256 MB | 256 MB | 768 MB? | 384 MB? | 不明 | 不明 |

| チップレット 構成 | 4 CCD (CCD 毎2 CCX) | 8 CCD (CCD 毎2 CCX) + 1 IOD | 8 CCD (CCD 毎1 CCX) + 1 IOD | 8 CCDと3D V-Cache (CCD毎1 CCX) + 1 IOD | 12 CCD (CCD 毎1 CCX) + 1 IOD | 12 CCD (CCD 毎1 CCX) + 1 IOD | 不明 |

| サポートメモリ | DDR4-2666 | DDR4-3200 | DDR4-3200 | DDR4-3200 | DDR5-5200 | DDR5-5600? | DDR5-6000? |

| メモリ チャンネル数 | 8 Channel | 8 Channel | 8 Channel | 8 Channel | 12 Channel | 12 Channel | 不明 |

| PCIe Gen サポート | 64 Gen 3 | 128 Gen 4 | 128 Gen 4 | 128 Gen 4 | 128 Gen 5 | 不明 | 不明 |

| TDP範囲 | 200W | 280W | 280W | 280W | 320W (cTDP 400W) | 320W (cTDP 400W) | 480W (cTDP 600W) |

解説:

Zen6の情報が初めてリーク

ひたすらマルチコア化を目指すAMD

Intelは使わない(使われない)マルチスレッド性能を上げるためにEコアを搭載しましたが、サーバーと同じダイを使うAMDはどうなのでしょうか?

少なくともZen4Cでは12CCDで128コアということになっていますので、1CCD当たり10.6コアと割り切れない数になります。

そのため、2種類のダイがあるのではないかと思います。

ひたすらマルチコアを目指してきたAMDですが、Zen5辺りでサーバーとのチップ共用化が難しくなってくるのではないかと思っています。

Zen5は256コア、Zen6は384コアと言われていますが、ハイブリッド設計になりますのでこちらも2種類以上のチップレットを組み合わせしてくる可能性はあると思います。

デスクトップ用途ではサーバーと違ってシングルスレッド性能が重視され、出来る限りクロックも上げなくてはいけません。

サーバーとチップを共用すると、将来的にクロックが十分に上げられなくなる限界点が来るのではないかと私は考えています。

まだどのような形になるのかはっきりした情報ではありませんが、なんにせよ。Zen6の名前が出てきたことは大きな進歩だと思います。

Ryzen 9000シリーズ

Ryzen 7000X3Dシリーズ

Ryzen 8000GシリーズAPU(GPU内蔵)

Ryzen 5000/4000シリーズ