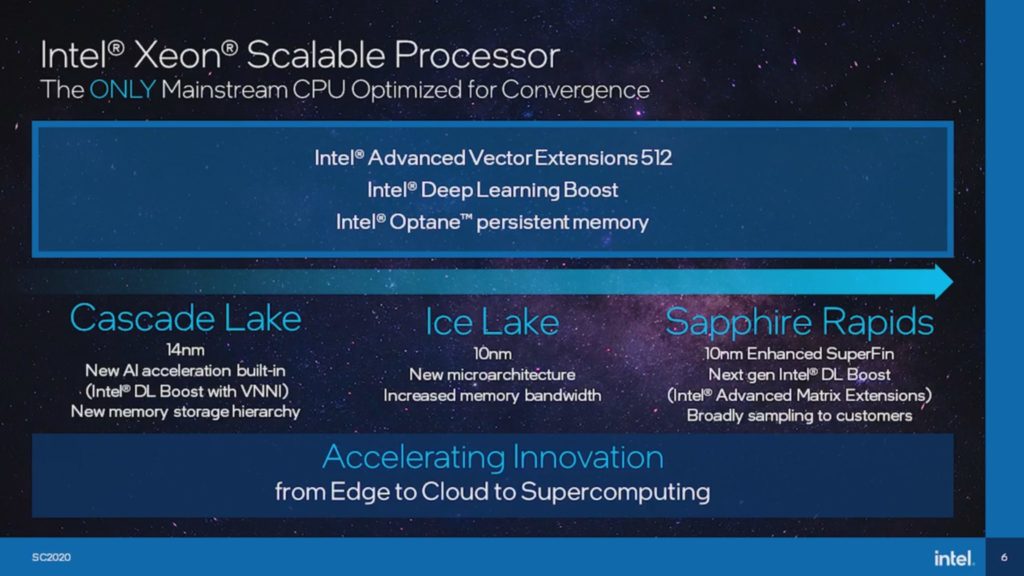

Intelは、次世代CPU「Ice Lake-SP Xeon Platinum」の新しい性能数値を発表し、AMDの第2世代EPYC Rome CPUと比較している。

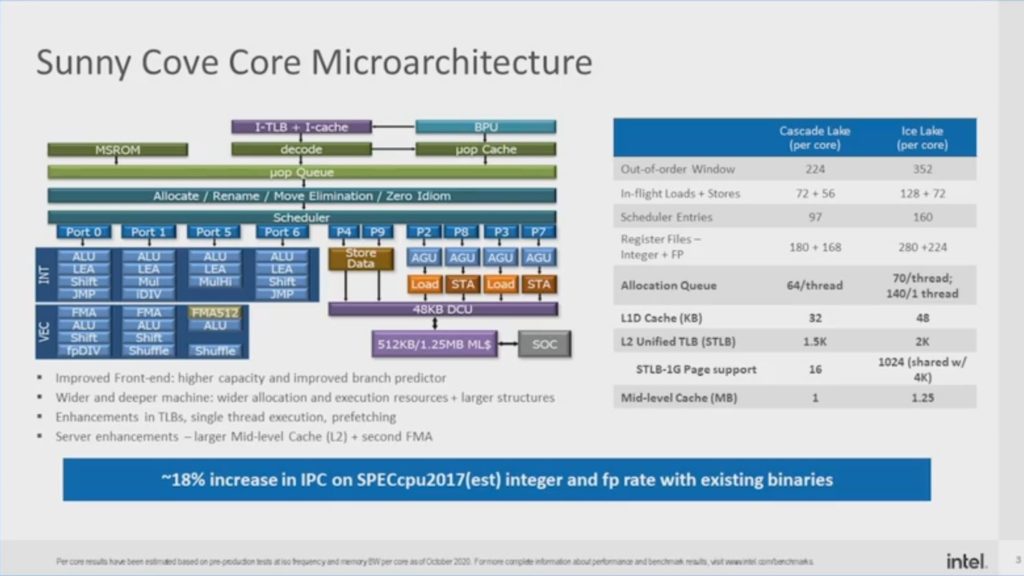

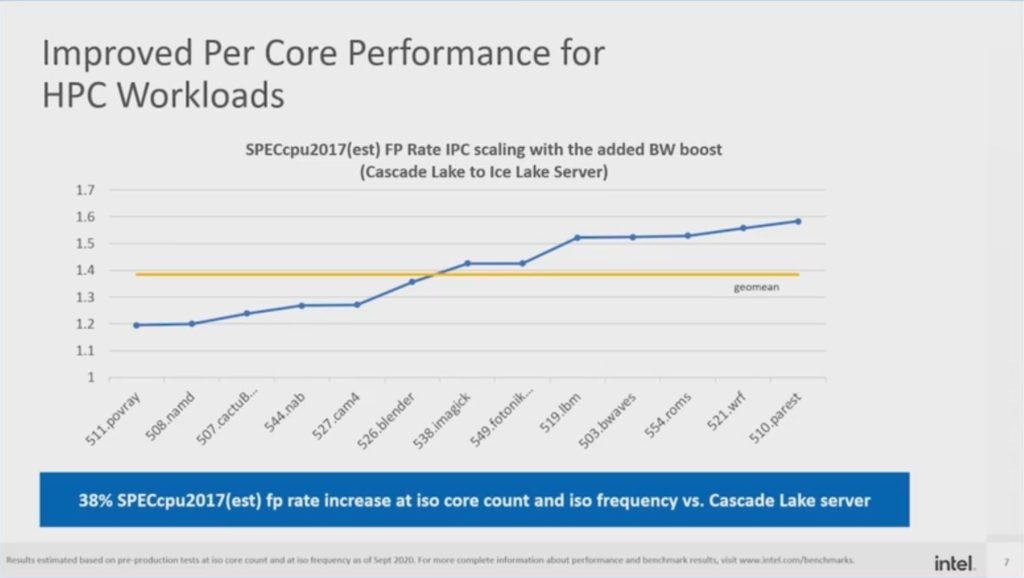

Intelによると、コアアーキテクチャを更新したIce Lake Xeon CPUは、前世代のCascade Lake Xeon CPUと比較して18%のIPCジャンプを実現し、AMDのハイコア数CPU製品との競合を可能にするという。

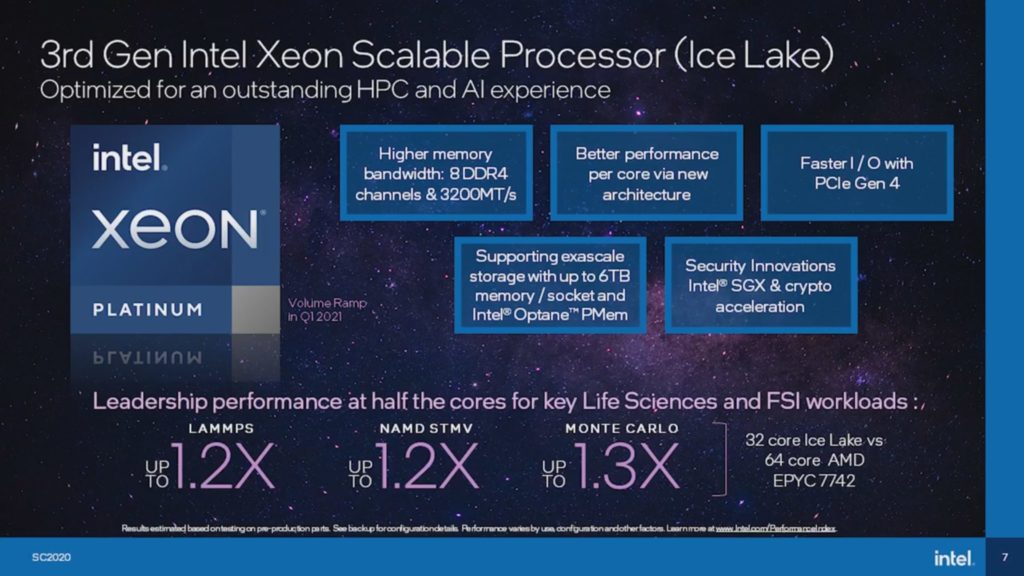

Intelは、32コアIce Lake-SP Xeon CPUは64コアのAMD EPYC Rome CPUを破ったが、裏があることを仄めかしている

SC20のプレゼンテーションの中で、インテルは、パートナーや顧客に対して、Ice Lake-SP Xeon CPU(第3世代スケーラブル・プロセッサ・ファミリー)は2021年第1四半期に量産を開始し、その後2021年半ば頃に正式に発売される予定であることを再確認しました。

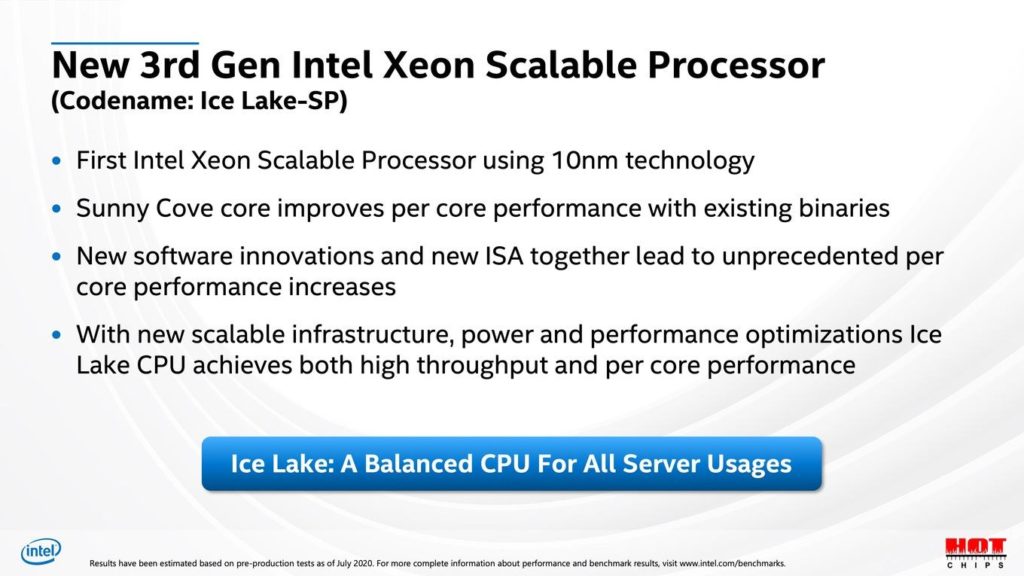

Intel Ice Lake-SP世代のXeon CPUは、10nmプロセスノードを使用し、新しいマイクロアーキテクチャと新しいプラットフォームを採用し、メモリ帯域幅の増加をサポートします。

※ クリックすると別Window・タブで拡大します。

Ice Lake-SP Xeon CPUは、Skylakeよりも18%のIPC向上を提供するSunny Coveコアアーキテクチャを使用することがわかっているので、それに基づいて、Intelは、コアあたりのパフォーマンスの向上、帯域幅の増加、PCIe Gen 4.0のフルサポート、ソケットあたり最大6TBのメモリサポート(Intel Optane PMem)を提供すると主張しています。

※ クリックすると別Window・タブで拡大します。

AMDの64コアEPYC 7742 CPUとの性能ベンチマークについては、インテルは、32コアのIce Lake-SP Xeon CPUは、主要なライフサイエンスおよびFSIワークロードにおいて、最大30%高速な性能を提供できると主張しています。

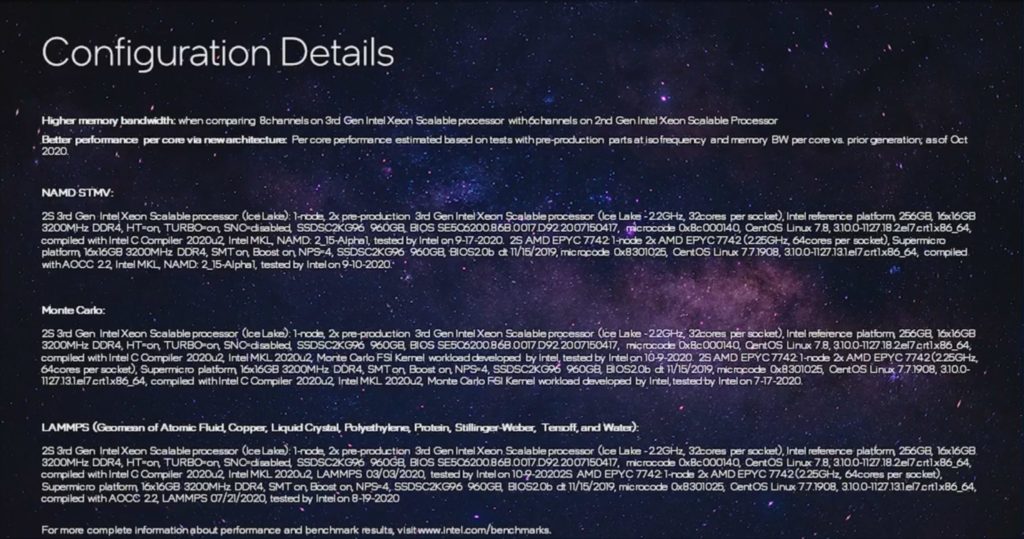

性能はNAMD STMV、Monet Carlo、LAMMPS内で測定された。

Intel Xeon Ice Lake-SP CPUは、1ソケットあたり32コア、64コアで構成されました。

実際の実行では、2台のIce Lake-SP Xeon CPUを合計64コア、128スレッドで使用したのに対し、2台のAMD EPYC 7742 Rome CPUを合計128コア、256スレッドで使用しました。

※ クリックすると別Window・タブで拡大します。

Intelプラットフォームは2.2 GHzのクロックで動作しており、合計256 GBのDDR4-3200 MHzメモリを搭載していたのに対し、AMD EPYCプラットフォームは2.25 GHz、256 GBのDDR4-3200 MHzメモリを搭載していた。

だから1つは、これはかなり公正なベンチマーク比較であると言うだろうが、AMD EPYCローマ64コアCPU上のこれらの20〜30%のパフォーマンス向上は、主にAVX512とAVX512以外の数字を比較することによって派生しています。

ここで報告されている 3 つのワークロードはすべて、Intel の AVX-512 命令を使用しており、大きな恩恵をもたらしています。

公平に見て、Intel は AVX-512 のワークロードでは、2 倍のコア数とより優れたプロセス ノードとアーキテクチャを持つチップを打ち負かし、かなり良い成績を収めています。

しかし、全体的な効率性と標準性能の面では、AMDのEPYCラインナップは、すべてのベンチマークでIntelを圧倒するだろう。

32コアのチップを64コアのチップと比較して、AVX-512を使っているという事実は、Intelがサーバーレースでどれだけ遅れをとっているかを示しており、AMDが第3世代のEPYCラインアップ、2021年第1四半期に予定されているMilanシリーズを発表する数ヶ月後には、状況はさらに白熱しそうだ。

Intel Ice Lake-SP「Next-Gen CPU」28コアダイ&Whitleyプラットフォーム詳細

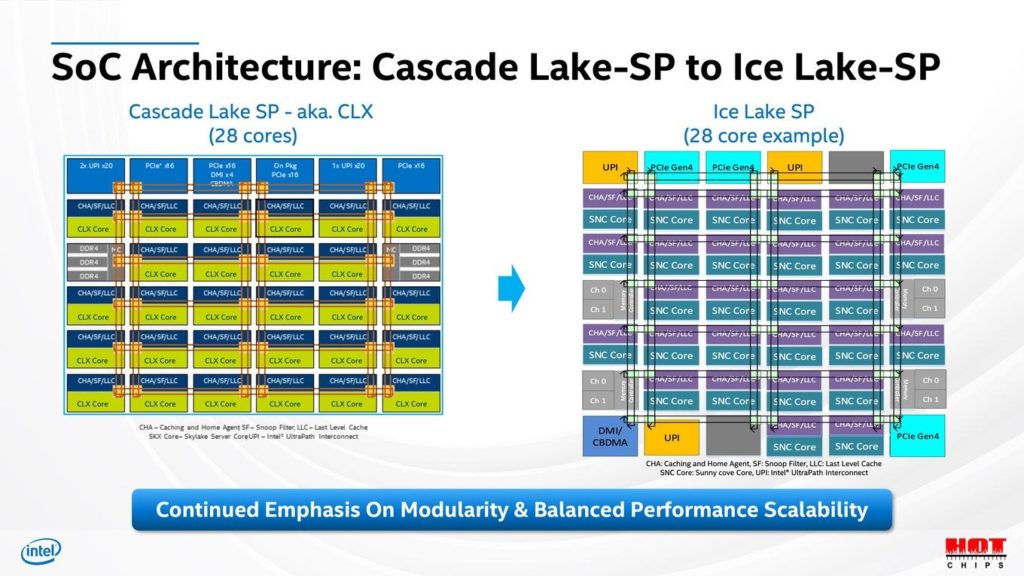

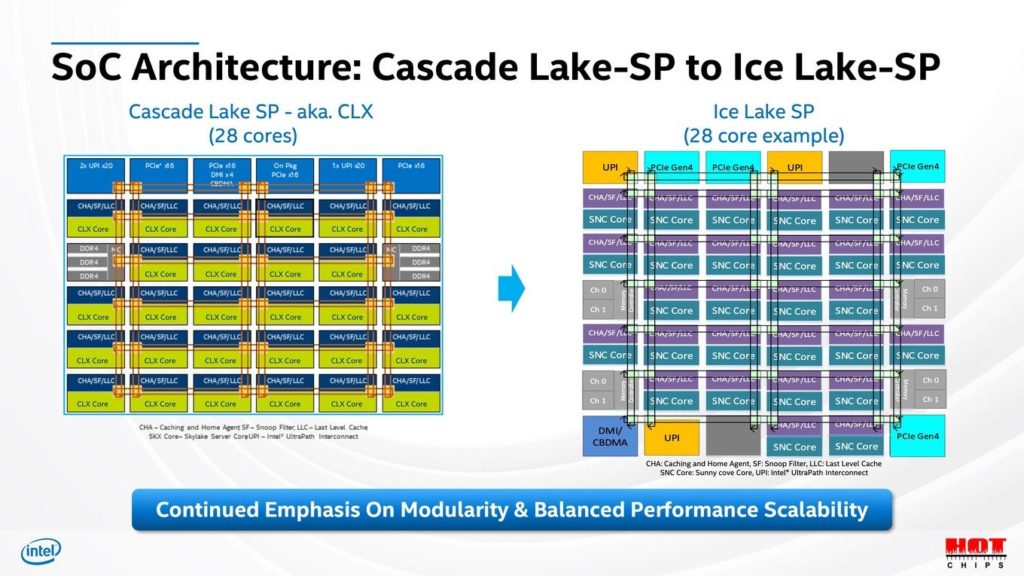

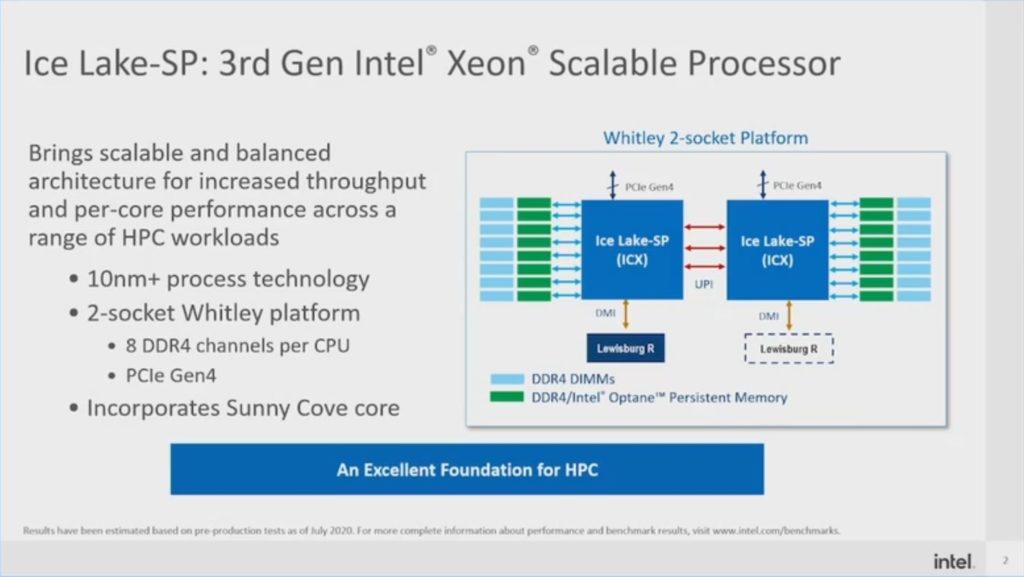

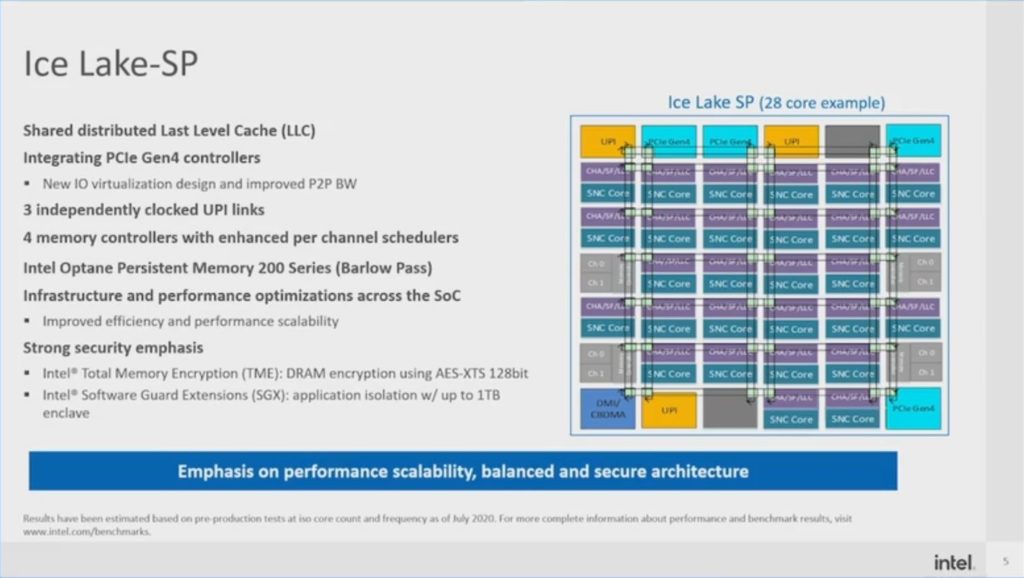

Ice Lake-SP 28コアCPUのブロック図を見てみると、このチップは28コアのCPUコアすべてを貫通する強化されたメッシュ・ファブリックの形で新しいインターコネクトを提供しています。

Ice Lake-SPダイは2つの4チャネルメモリコントローラを搭載していますが、Cascade Lake-SPダイは2つの3チャネルメモリコントローラを搭載しています。

※ クリックすると別Window・タブで拡大します。

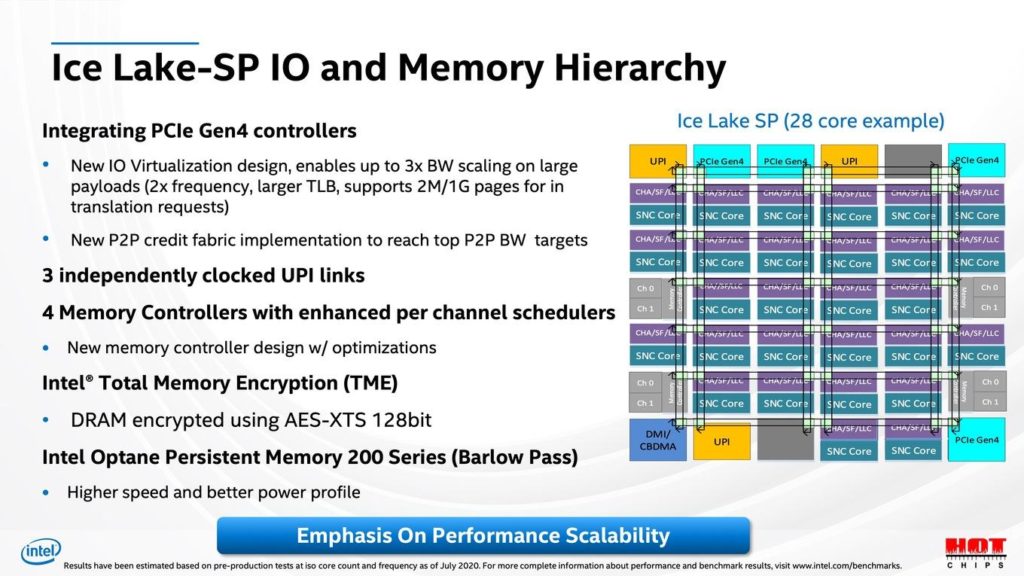

Intel Ice Lake-SPプロセッサは、4つのPCIe Gen 4コントローラを搭載しており、それぞれが16のGen 4レーンを提供し、28コアダイ上で合計64レーンを提供します。

Cascade Lake-SPチップはヘキサチャネルメモリをサポートし、Ice Lake-SPはWhitleyプラットフォームでオクタチャネルメモリをサポートします。

このプラットフォームでは、最大でDDR4-3200MHzのメモリ(第2世代のパーシステントメモリをサポートするソケットあたり16 DIMM)をサポートすることができる。

※ クリックすると別Window・タブで拡大します。

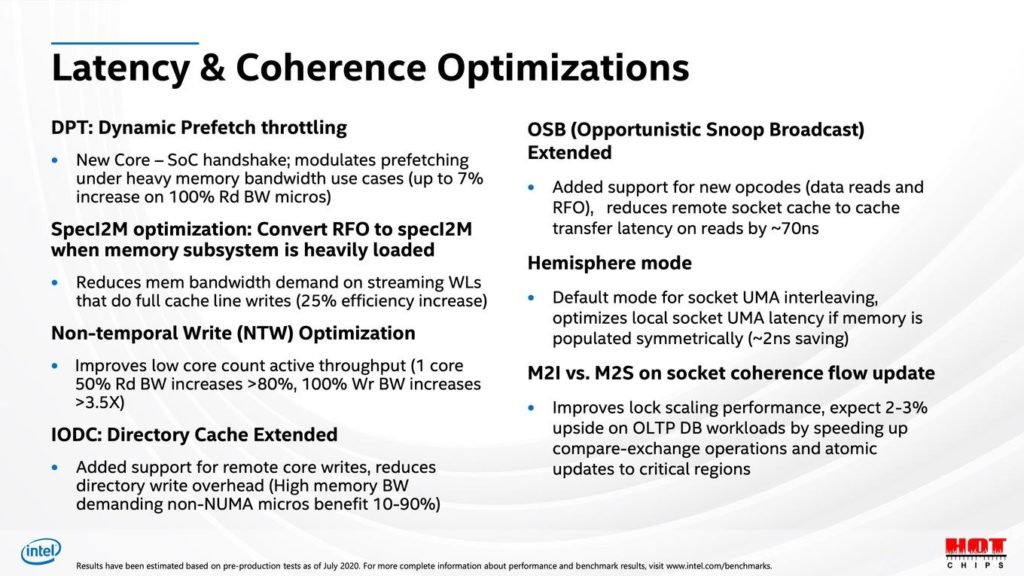

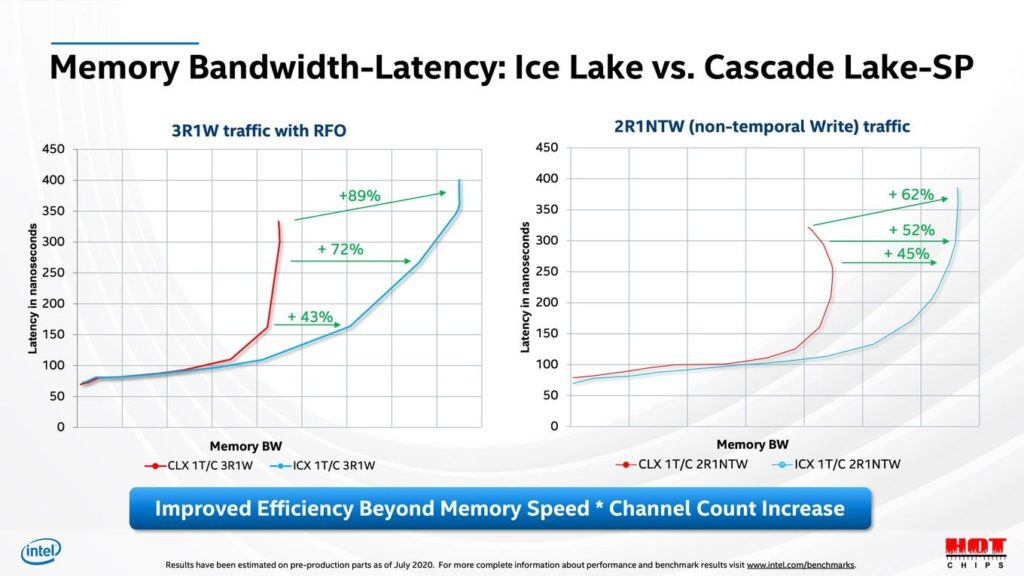

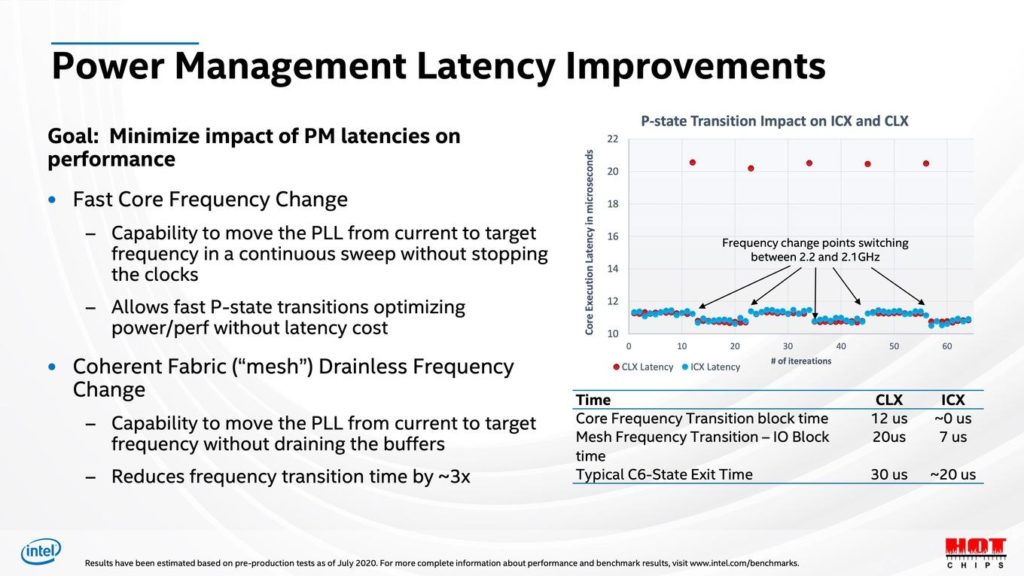

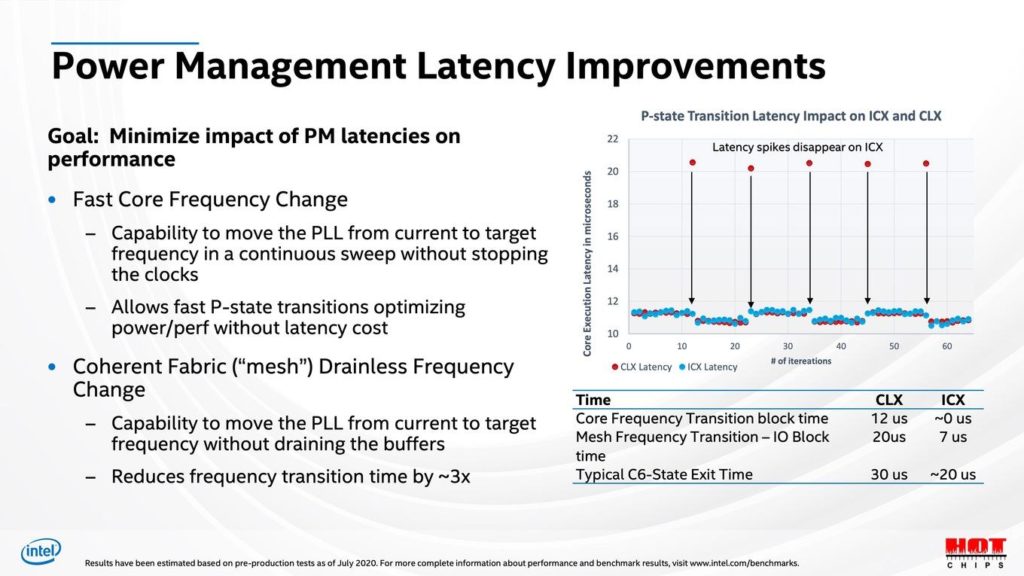

Intelは、Ice Lake-SPチップにもレイテンシとコヒーレンスの最適化の調整をしている。

しかし、8チャンネルのメモリインターフェイスとDIMMの高速化により、メモリ帯域幅のレイテンシが大幅に向上していることがわかります。

※ クリックすると別Window・タブで拡大します。

Intel Ice Lake-SP「次世代CPU」新インターコネクト基盤

Intelは、標準的なMeshインターコネクトに加えて、Ice Lake-SP Xeon CPU用のインターコネクト設計をさらに拡張した。

新しいコントロールファブリックとデータファブリックは、チップのコアと異なるコントローラに接続するだけでなく、チップ自体のデータフラワーと電力制御も管理する。

これらの新しいインターコネクトは、第3世代のCooper Lake-SPチップよりもさらに低いレイテンシと高速なクロック更新を実現する。

例えば、Cascade Lake-SPチップでは、コア周波数の遷移に12us、メッシュ周波数の遷移に20usかかる。

それに比べてIce Lake-SPでは、それぞれ1us以下、7us以下で済んでいます。

※ クリックすると別Window・タブで拡大します。

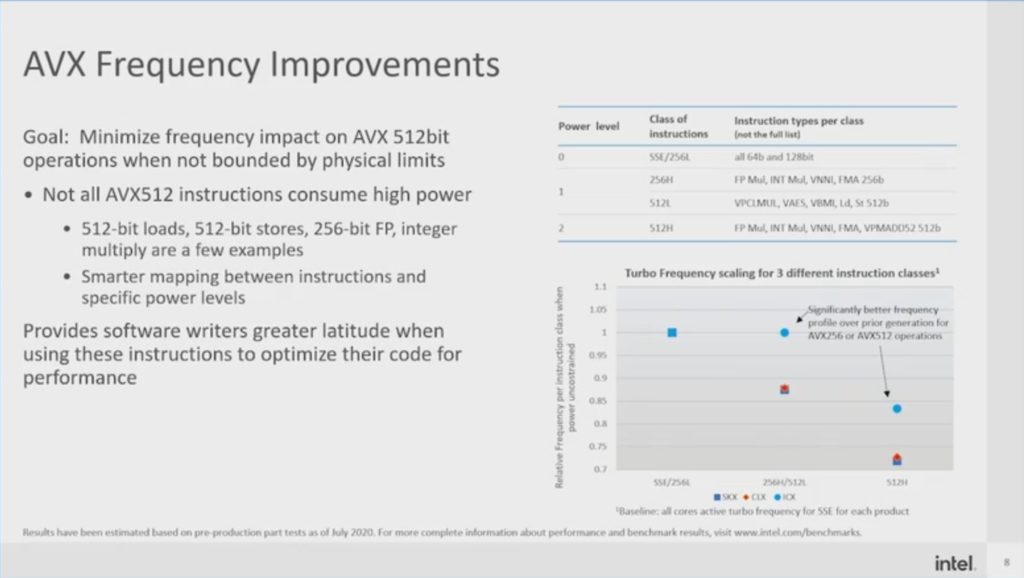

周波数ドレインが少ないということは、Cascade Lakeよりも効率が高いことを意味します。

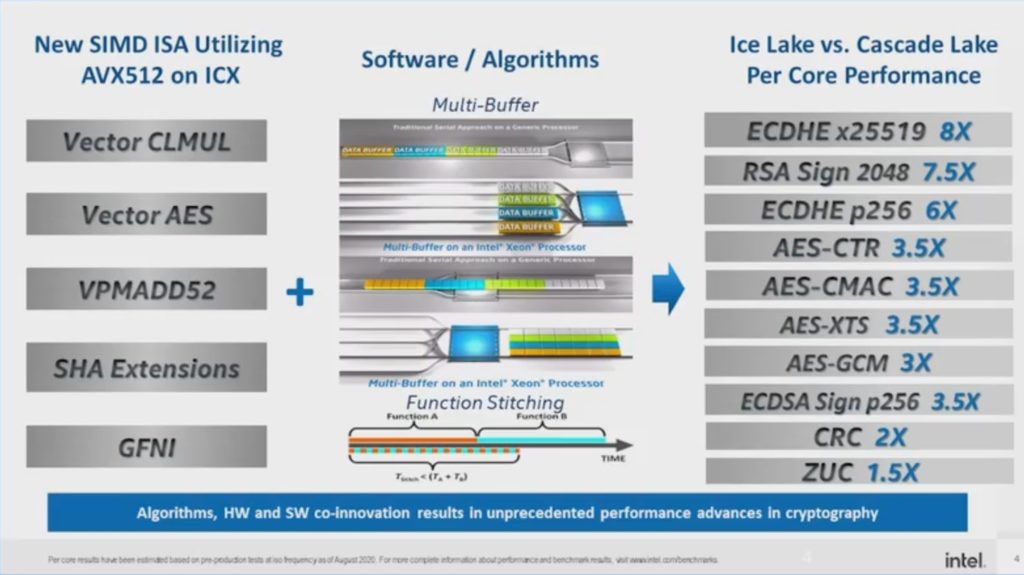

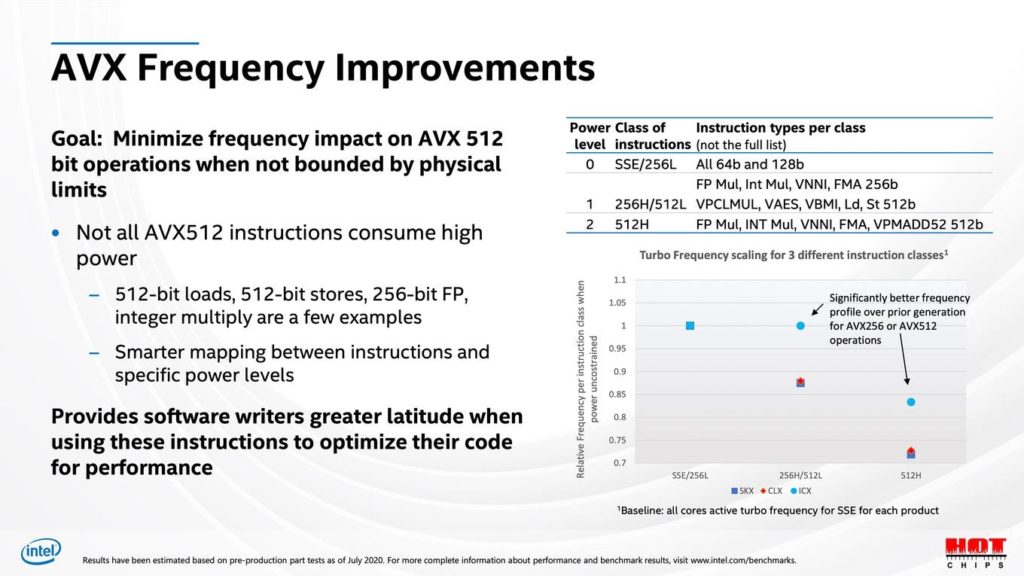

すべての AVX-512 ワークロードがより高い電力を消費するわけではないので、Ice Lake-SP は AVX の周波数も向上します。

これは AVX-512 に限ったことではありません。

Ice Lake-SPのAVX-256命令でさえ、Cascade Lake CPUよりも優れた周波数プロファイルを提供します。

10nmが提供する主要なアップグレードには、以下のようなものがある。

- 14nmと比較して2.7倍の密度スケーリング

- 自己整列型クアッドパターニング

- オーバーアクティブゲートへのお問い合わせ

- コバルトインターコネクト(M0、M1

- 第1世代フォベロス3Dスタッキング

- 第二世代EMIB

Intel Ice Lake-SPのラインアップは、AMDの強化された7nmベースのEPYC Milanラインアップと直接競合することになります。

解説:

Ice Lake-SP Xeonの情報

こちらはDesktopのCypress Coveと違って本物の10nm Sunny Coveになります。

Intelにとっての本丸とはXeon Scalableで、デスクトップは単なるオマケです。

それは虎の子の10nmを惜しげもなく投入していることからも明らかではないでしょうか。

もちろんIce Lake-SP Xeonの方が大掛かりで高価なシステムになっています。

全く同じではないです。

IPCは18%向上しているといわれますが、その一部はRocket Lakeとして我々の前に姿を現すと思います。

さて、記事の内容ですが、32コア64スレッドのIce Lake-SP Xeonは64コアEPYC Romeをベンチマークで破ったとされていますが、これはAVX-512を使った数字であり、そうでないベンチマークについては当然のことながら倍のコア数を誇るEPYCにかなうはずがありません。

※ AVX-512とは512ビットのベクトル処理機能を備えた拡張命令のこと。Intel Xeon Phiプロセッサ/コプロセッサ、Intel Xeon Scalableプロセッサなどで利用できる。

AVX-512に関しては様々な批判がありますが、intelが特定の用途で優位性を確保するには必要な仕組みだと思います。

事実、AMDのEPYC Romeに通常の用途では負けてしまっているという現状があります。

さて、Ice Lake-SP Xeonが10nmで発売されるならデスクトップにも下ろしてくれよと思う方もいると思いますが、サーバー用のプロセッサは相対的にデスクトップのPCよりクロックが重視されませんので、コストが見合わない他にはクロックが上がらないのかなとも思いますね。

いずれにしても来年からようやく、総ての分野でPCI Express4.0に対応するIce Lake世代の製品に切り替わることになります。

ゲーミング向けデスクトップは残念ながら8コアまでですが、その理由は明かされるのかな?と疑問に思います。

まあ、殻割写真が出回れば私の言う「ダイサイスが大きくなりすぎたから」と言うのが理由なのかどうかわかると思いますが。

RyzenはintelのCoreよりも一回り大きいですが、物理的形状が制約を与えたのかどうかと言うのは気になるところです。

Alder Lakeは縦長になっていますしね。

Core Ultra 200Sシリーズ

ソケットLGA1851

※ 末尾にFがついているモデルはGPUがありませんのでご注意ください。