9月に向けて、一つ確かなことがあります。

Appleの2019 iPhone 11ラインアップには、TSMCのN7 +ノードで製造された真新しいプロセッサが搭載されます。

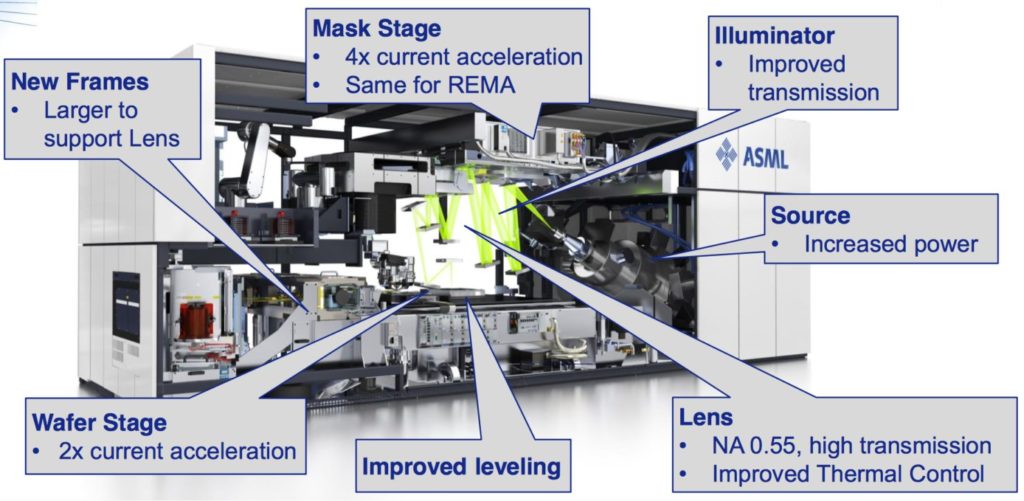

N7 +ノードは、A13の特定のレイヤーに極端紫外線リソグラフィー(EUV)を使用し、チップの前身であるA12よりもパフォーマンスと電力効率を改善します。 ただし、TSMCは将来を見据えています。

同社は、次世代のリソグラフィ技術、パッケージング手法、およびパフォーマンスノードを積極的に開発しています。

今日、私たちは今後数年間、台湾のファブに何を期待するかについて多くの詳細を入手しました。

詳細については以下をご覧ください。

TSMCのN7 +プロセスは一部のレイヤーにEUVを使用します–台湾のFabはN6製造プロセスでEUVを介してより多くのレイヤーを実装します

ほとんどの人はTSMCのN7およびN7 +ノードについてのみ知っていますが、現実には、工場には他にもノードがあります。

これらの他のノードは、会社が開発したさまざまな製造プロセスの世代間のシフトを表しており、前任者の延長でもあります。

今日、TSMCの6つのパフォーマンスノードと5つのパッケージングテクニックの詳細を確認しました。

ノードは2023年まで延長され、技術はモバイルSoCから5Gモデムおよびフロントエンドレシーバーにまで拡張されます。

TSMCは今年初めに忙しいVLSIシンポジウムを開催し、1.20Vで4GHzの周波数に対応できるカスタムビルドのオクタコアA72チップレットを展示しました。

TSMCは、3nm以上の伝導用のチャネル材料として二硫化タングステンも導入しました。

今年のセミコンウエストでのTSMCのプレゼンテーションの後、ウィキチップの良き人々は、同社のプロセスノードとパッケージング計画を統合しました。

N7+はTSMCの最初のEUVベースのノードですが、この技術で製造されたチップは、EUVを利用したTSMCの最先端のシリコンではありません。

N7+の詳細については、こちらをご覧ください。

N7の後のTSMCの最初の「フル」ノードは、N7のIPと設計を活用する3つの中間ノードを持つN5です

N7ノードに続くのは、前者のDUVベースの最適化であるTSMCのN7Pプロセスです。

N7PはN7のデザインルールを使用し、N7とIP互換性があり、FEOL(フロントエンドのライン)を使用します

MOL(Middle-of-Line)の改善により、パフォーマンスが7%向上するか、電力効率が10%向上します。

N7+はTSMCがEUVを使用した最初の製造プロセスであり、すべてのレイヤーに高度な低波長リソグラフィーを使用していません。

その結果、設計プロセスはN7Pをわずかに上回ります。

TSMCのN7向けの最初の真のEUV実装は、ファブのN6処理ノードです。

N6はN7と設計およびIP互換ですが、主な強みはセルアバトメントにあります。

※ アバトメントとは隣接する回路のマージ可能な要素をマージする設計上の手順のこと。詳しくはこちらを参照してください。私も設計の専門家ではありませんので、私の理解が間違っていたら指摘してください。

これは、TSMCの最初のノードであり、連続ポリオーバー拡散エッジプロセス機能を使用してロジックブロックをレイアウトし、レジスタパスの最適化とデッドタイムの削減を可能にします。

この改善により、N6を使用するプロセッサーは、N7+によって作成されたチップより18%密度が向上します。

N6は2020年にリスク生産を開始する予定です。

※ リスク生産とはFabの側が投資を行って(リスクを負って)生産すること。Fabの側がリスクを追わなかったらどこが負うかというと客の側。しかし、あまりにリスクが高すぎてどこも応じなかったので、Fabの側がリスクを負うのが一般的の様だ。

N5と呼ばれるTSMCの5nmノードのリスク生産は4月4日に開始され、台湾からの1つのレポートでは、このプロセスは来年(2021年)後に大量生産されることを示唆しています。

TSMCは2020年に生産量が増加すると予想し、N5はN7の最初の真の後継であり、プロセスを通じて製造されたチップはその大半の層にEUVを使用するため、ファブはプロセスの開発に大規模に投資しています。

N5の製造原理を使用して製造されたチップは、N7で製造されたチップの2倍の密度(171.3MTR /mm²)であり、ユーザーはN7より15%高いパフォーマンスを実現するか、消費電力を30%削減できます。

ただし、FEOLおよびMOLの最適化はN5Pで行われます。

これらにより、N5Pはパフォーマンスを7%、消費電力を15%改善します。

物事の見た目から、TSMCは将来の行動を鋭く計画しており、工場はその計画の詳細を共有することをためらっていません。

N5ノードは注意が必要なノードです。

このノードで製造されたチップは、TSMCのチップレットアプリケーションが完全に機能するように、小さな領域で十分なコンピューティングパワーを生成するためです。

何か意見がありますか? 下記のコメントセクションでご意見をお聞かせください。引き続きご注目ください。

最新情報をお届けします。

ソース:wccftech - TSMC’s True EUV Lithography Will Be On N5 Node For 2x Transistor Density

解説:

ついにN5ノードの話が出てきました。

N5ノードは7nmEUVの2倍の密度を実現できるということのようです。

TSMCには7nmEUVのほかに7nmと互換性のあるN6(6nm)があり、AMDはこちらを利用します。

この記事はwccftechの元記事では「モバイル」カテゴリに含まれており、PC向けでないことがすでに明示されています。

N5ノードは資金のたっぷりあるスマホ向けのSoCのみに使用されるようです。

intelが10nm(TSMCの7nmに相当)を出したときにはすでに周回遅れになっていることがほぼ確定しているというなんとも切ない話です。

さらに7nmを出したとしてもAMDは6nmに移行しており、性能的に追いつけるのかどうかは微妙な状態だと思います。

こんな感じでしばらくintelは製造技術のビハインドを負うことになります。

TSMCはすでに台湾の新竹市に3nmの研究施設を集中させており、次世代に追いつけるかどうかは微妙な状況でしょう。

intel7nm(TSMCの5nmに相当)の先の話は聞こえてきませんので、依然としてintel製品は巨大なハンデを負っていることは事実だと思います。

こうした状況の中でintelがどこに向かうのかというのは私も注目しているところです。