2030年以降は?

インテルとは異なり、TSMCはASMLの次世代High-NA極端紫外線(EUV)チップ製造ツールの使用をいつ開始する予定かを発表していないため、当然ながらその意図について多くの憶測を呼んでいる。

1カ月前、あるアナリストは顧客向けメモに、TSMCは1nmプロセス技術の生産を開始するまでHigh-NAツールの使用を待つだろうと書いた。

今週、DigiTimesは、TSMCSが次世代ツールの使用を1nmまで待つことを確認したファブ・ツールメーカーの独自の情報筋の話を追加した。

TSMCの遅れはコスト懸念に帰結する可能性がある。

セミアナリシスのアナリストは、TSMCがHigh-NA EUVシステムの使用を開始するのは1nmクラスのプロセス技術(A10として知られる)になってからだと見ている。

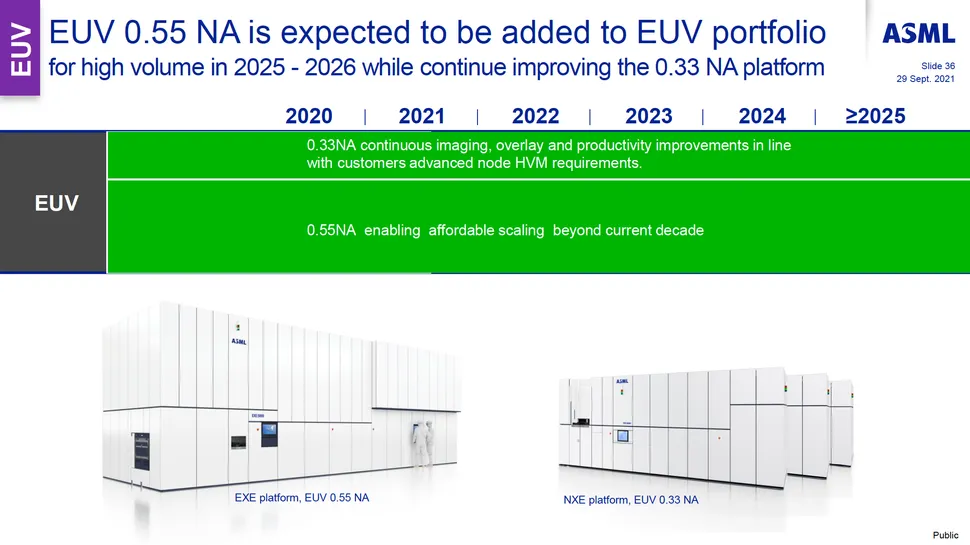

インテルは、18A以降のプロセス技術にHigh-NA EUVツールを使用する予定であり、これはおそらく2026年から2027年にかけてEUVツールの使用が開始されることを意味する(ただし、インテルはこの時期を正式に確認していない)。

一方、ロジックとメモリーの主要メーカーはすべて、研究開発(R&D)のためにHigh-NA EUVツールを購入しているが、導入スケジュールは公表していない。

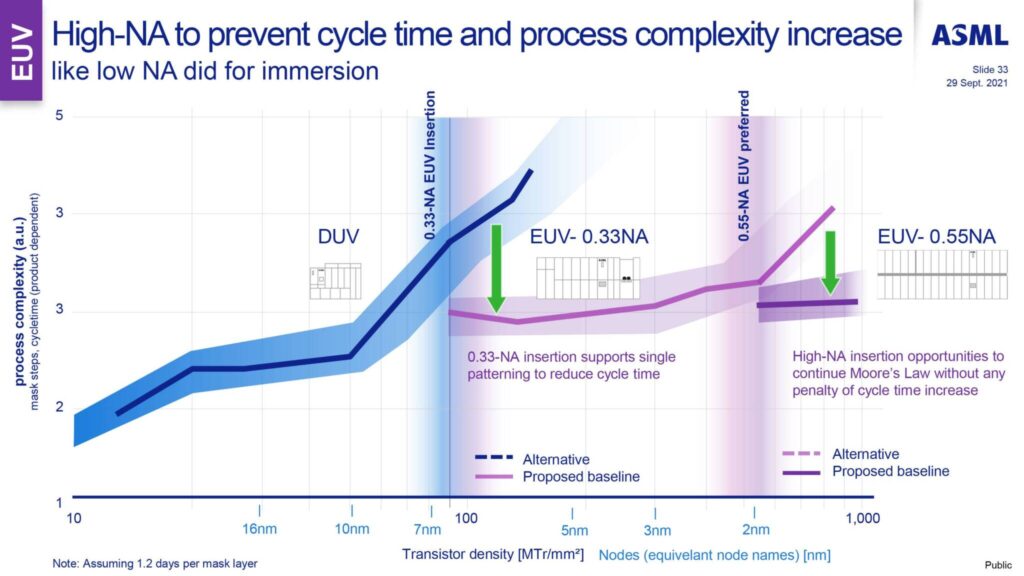

High-NA EUVリソグラフィ・ツールは、1回の露光で8nmの寸法を達成することを可能にし、既存のLow-NA EUVツールの13nmを大幅に改善する。

しかし、既存のEUV露光装置は、ダブルパターニングで8nmの解像度を達成でき、表向きには全体的なコストを下げることができるため、すべてのチップメーカーがこれらの露光装置の商業展開を急いでいるわけではない。

高NA EUVツールはまた、非常に高価であり、その巨大なサイズに対応するために既存の製造設備を大幅に変更する必要がある。

※ 画像をクリックすると別Window・タブで開きます。

念頭に置いておくべきことの1つは、計画は既存の技術の性能だけでなく、その他の市場要因に基づいて変更される傾向があるということである。

つまり、TSMCがすぐにHigh-NA EUVツールを投入するようには見えないかもしれないが、計画は正式なものではないし、仮にそうであったとしても、同社の計画は常に変更される可能性がある。

解説:

TSMCの1nmは2030年か?

2nmが2025年予定で、3nmはすでに量産開始しています。

Intelが18Aの予定を発表していますが、あれはTSMCのプロセスに直しているだけで本当に2nm以下というわけではありません。

IntelとTSMCではプロセスルールの数字が同じでも全然密度が違うのでシェアの大きいほうに合わせるというのは合理的な判断だと思います。

2nmから1nmまでは5年も期間が空きますが、その間、配線技術や素材を見直すことによって密度を上げていくという計画のようです。

2nm世代は2nm+とかいろいろ後ろにつくことになるかもしれませんね。

今回の話は「TSMCSが次世代ツールの使用を1nmまで待つことを確認したファブ・ツールメーカーの独自の情報筋の話を追加した。」がソースのようです。

日本も熊本がTSMCのおひざ元になりましたので、無関係な話でもないと思います。

ここにきて、かなり半導体製造技術の微細化が減速しましたが、皮肉なことにもはやマスでも最先端でもなくなったPCのパーツには最先端のプロセスは使われていません。

2nm以降の改良プロセスがどの程度準備されているかにもよりますが、あと数年は現行の技術を使いながら、対応できるのではないかと思います。

AMDの最新はPhoenixの4nmです。

3nmはまだ使っていないので、多少の余裕はあるということになります。

むしろ困っているのはスマホのSoCのほうではないかと思います。