AMD、第2世代3D V-Cacheについて言及

AMDは、Ryzen 7000X3Dシリーズに採用されている新しい3D V-Cache技術に関する新たな詳細を確認しました。

Ryzen 7000X3Dシリーズの発売からほぼ1週間が経ちました。AMDはレビュアーに対してオープンブックであり、消費者が知りたいと思うような必要な詳細をすべて提供しました。

しかし、エンドユーザーにとってはそれほど重要ではないかもしれないが、それでも技術者コミュニティにとっては非常に興味深い詳細がいくつかあった。

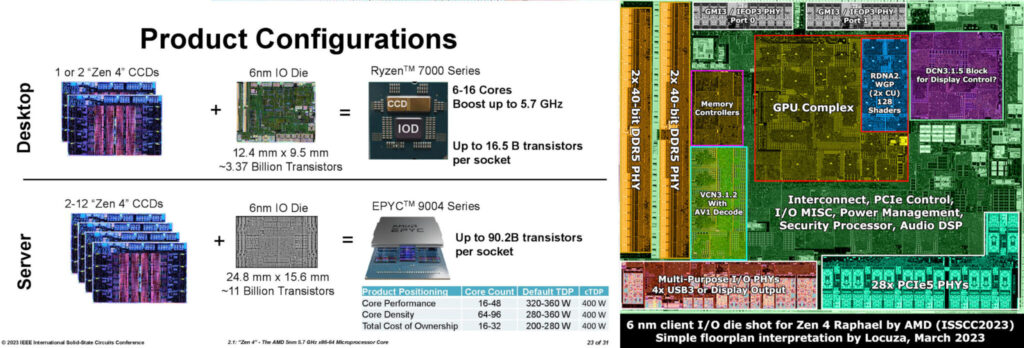

週末、AMDは3D V-Cache技術に関するさらなる詳細を提供するとともに、Raphaelのコードネームで呼ばれるデュアル8コアCPUの第3チップレットである新しいI/Oダイの写真を初めて公開しました。

これらの詳細の一部は、Tom's Hardwareが同社に直接問い合わせたもので、残りの詳細は2023年の国際固体素子回路会議(ISSCC)で確認されたものです。

Ryzen 7000シリーズの3D V-Cacheは、Level 3キャッシュをチップレット1つに対して最大96MBまで拡張する。

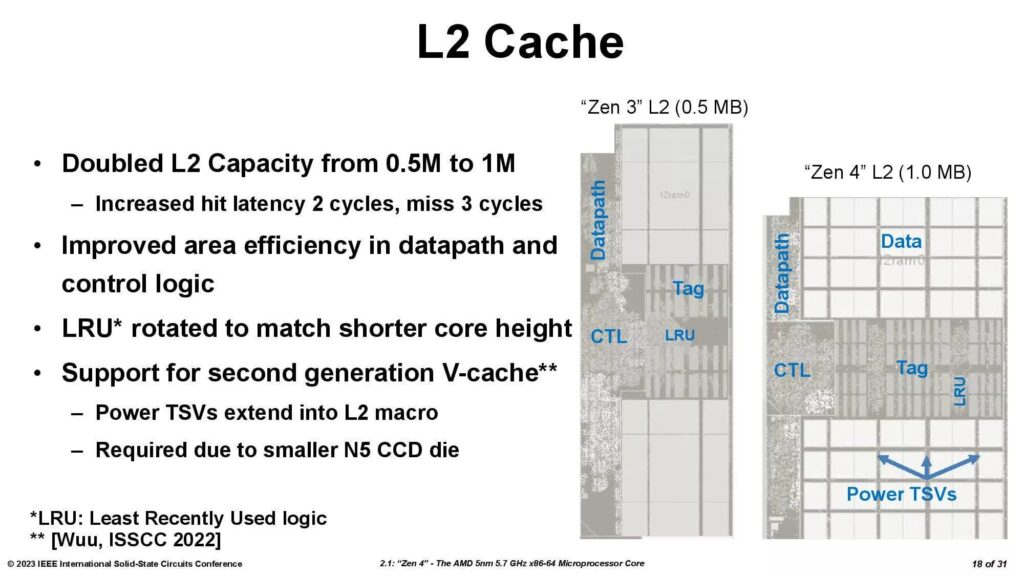

キャッシュ自体は7nmプロセスノードで設計されており、5nmのZen4 CCDの上に配置されています。

第2世代のキャッシュ・ダイは、同じトランジスタ数を維持しながら、第1世代よりも実際に小さくなっています。

これは、トランジスタ密度が114.6Mから130.6Mtr/mm²に増加したことを意味します。

第2世代3D V-Cacheテクノロジー AMD Ryzen 9 7950X3D

| 第二世代 7nm 3D V-Cache ダイ | 第一世代7nm 3D V-Cache ダイ | 5nm Zen 4 Core Complex ダイ (CCD) | 7nm Zen 3 Core Complex ダイ (CCD) | |

| サイズ | 36mm2 | 41mm2 | 66.3 mm2 | 80.7mm2 |

| トランジスタ数 | 最大47億 | 47億 | 65.7億 | 41.5億 |

| MTr/mm2 (トランジスタ 密度) | 最大1億1300万 | 最大1億1460万 | 最大9900万 | 最大5140万 |

AMDはまた、新しいキャッシュが2.5 TB/sに達する高い帯域幅を持つことを確認しました。

これは、5800X3Dのキャッシュダイ設計と比較して、25%または0.5TB/秒の改善です。

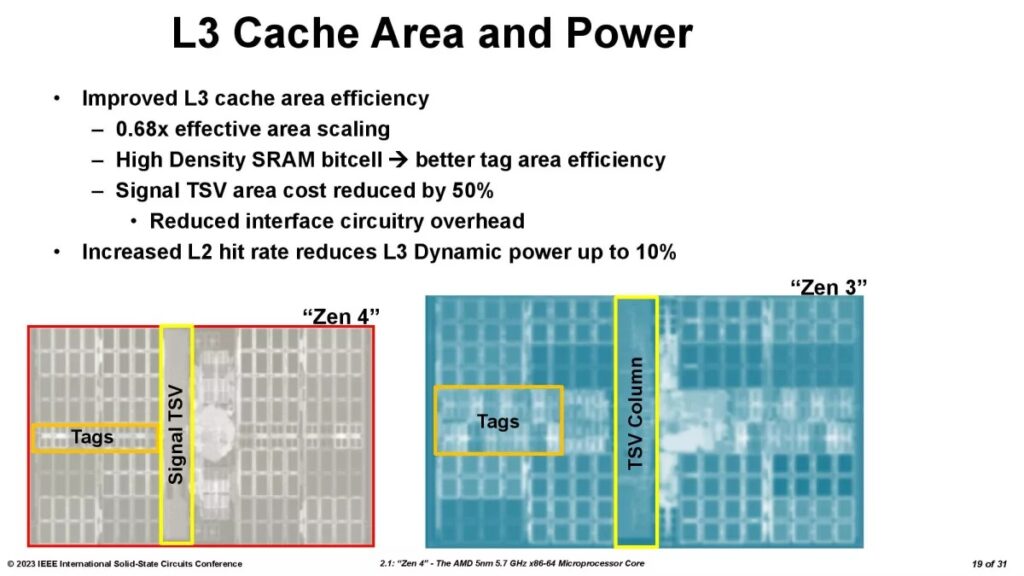

さらに、設計の変更に伴い、AMDはTSV(Through Silicon Vias)接続も変更する必要がありました。

AMDはTSVの面積を50%縮小しなければなりませんでした。

AMDはRyzenとEPYCシリーズで同じZen4 CCDを使っているが、それに合わせてI/Oダイをコンシューマ向けとデータセンター環境向けに変更している。

コンシューマ向けのI/Oダイの写真もスライドデッキで共有されている。

このダイショットはISSCCのプレゼンテーションに追加され、ハードウェア探偵Locuzaによって素早く分析され、適切な注釈が付けられた。

統合GPUの大きさを示しており、確かに128コアに制限されていることが確認できる。

さらに、I/OダイにはGMI(Global Memory Interconnect)ポートが2つしかないため、このチップレットではトリプルCCD構成が不可能であることも確認されています。

解説:

同じ3D V-Cache なんだからみんな同じ、そう思っている時期が私にもありました。

3D V-Cache CCDの詳細が明らかに

キャッシュ自体は7nmで製造プロセス自体は5800X3Dと変わっていませんが、トランジスタの密度か変わっているとのこと。

コンシュマー向けIODは2CCDしか接続できないともあります。

速度も向上しており、さらにキャッシュのヒット率も上がっているようです。

同じX3Dですが、5800X3Dと比べると随分パワーアップしているようです。

キャッシュダイのサイズが小さくなっているのはちょっと驚きました。

Ryzen 9000シリーズ

Ryzen 7000X3Dシリーズ

Ryzen 8000GシリーズAPU(GPU内蔵)

Ryzen 5000/4000シリーズ