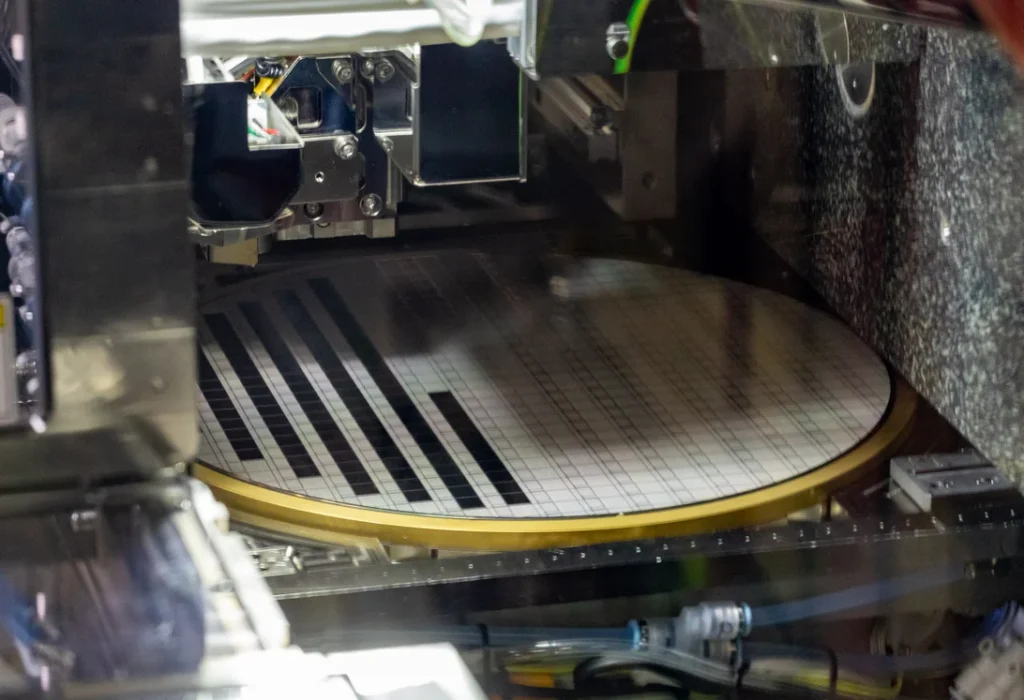

CNETは、米国アリゾナ州にあるチップメーカーのFab 42でテスト・生産されている、複数の次世代Intel Meteor Lake CPU、Sapphire Rapids Xeons、Ponte Vecchio GPUのダイショットを初めて撮影しました。

アリゾナ州のFab 42で撮影されたインテルの次世代CPU「Meteor Lake」、Sapphire Rapids Xeons、Ponte Vecchio GPUのダイショット写真

CNETのシニアレポーターであるスティーブン・シャンクランドは、米国アリゾナ州にあるインテルのFab 42を訪れ、このダイショットを撮影しました。

この工場では、コンシューマー、データセンター、ハイパフォーマンス・コンピューティング分野向けの次世代チップを製造しており、すべてのマジックがここで行われています。

このFab 42では、10nm(インテル7)および7nm(インテル4)プロセスノードで製造されたインテルの次世代チップが扱われます。

これらの次世代ノードを利用する主要製品には、Meteor Lakeクライアント・プロセッサー、Sapphire Rapids Xeonプロセッサー、HPC用Ponte Vecchio GPUなどがあります。

Intel 4搭載のMeteor Lake CPUはクライアントコンピューティング向け

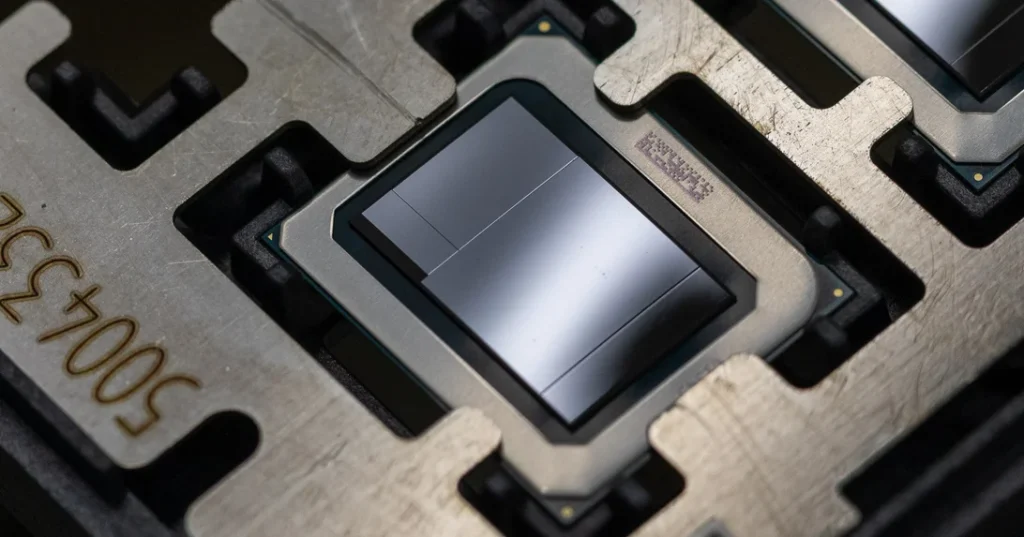

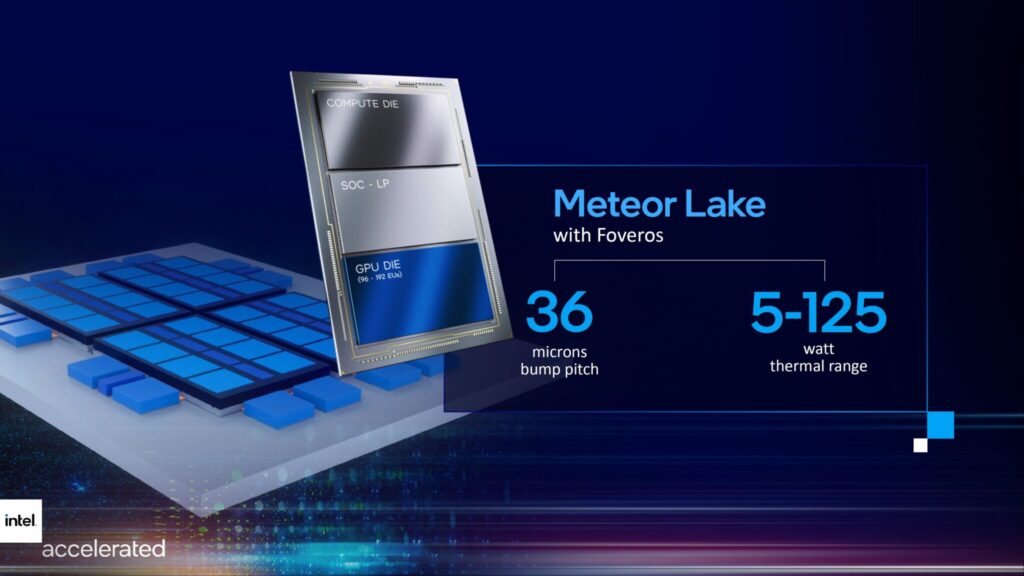

最初にご紹介するのは、Meteor Lakeです。2023年にクライアントのデスクトップPCに搭載されるMeteor Lake CPUは、Intel初の真のマルチチップレット設計となります。

CNETは、最初のMeteor Lakeテストチップの写真を入手することができました。

この写真は、Intelが2021年のイベント「Architecture Day」で予告したレンダリング画像と驚くほど似ています。

上の写真のMeteor Lakeテスト車両は、Forverosパッケージデザインが正しく、期待通りに機能することを確認するために使用されます。

Meteor LakeのCPUは、IntelのForverosパッケージング技術を利用して、チップ上に統合された様々なコアIPを相互に接続します。

Intel Meteor Lakeテストチップは、次世代Core CPUの最終生産に向けてChipzillaを準備します。(ソース:CNET)

ダイには4つのチップレットがあり、同一基板上で接続されています。Intelがレンダリングで示した内容からすると、一番上のダイが「Compute Tile(コンピュートタイル)」、真ん中のダイが「SOC-LPタイル」、一番下のダイが「GPUタイル」となるはずだ。

しかし、ダイのサイズからすると、それはうまくいかない。真ん中のダイがコアを搭載したメインのComputeタイルで、その下の小さいダイがIOを搭載したSOC-LPタイルになる可能性がある。

一番上のダイはGPUで、その隣の小さいダイは別のキャッシュや別のIOタイルになるかもしれません。

これらはテストチップであり、最終的な設計は異なる可能性があるため、現時点では純粋な推測に過ぎません。

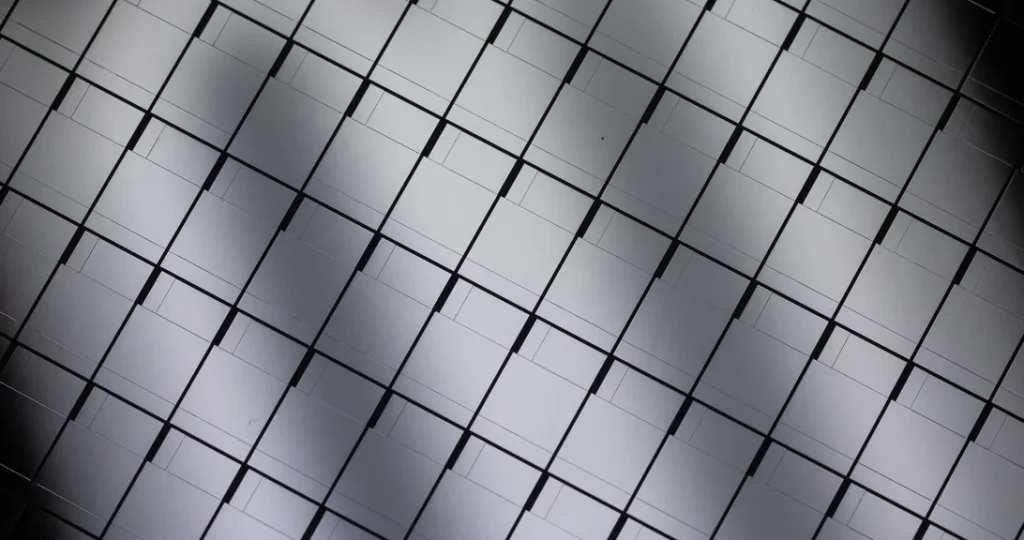

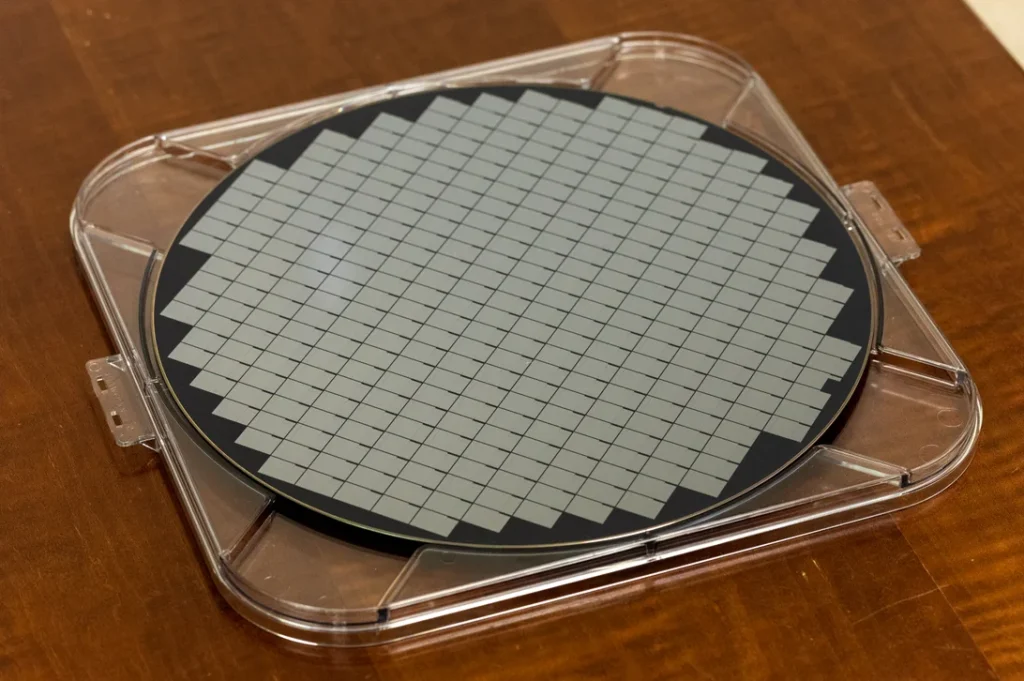

また、Meteor Lakeのテストチップは、300mmの大きさのウェハを初めて見ることができます。

このウェハは、チップ上の相互接続が意図したとおりに動作することを確認するためのダミーダイであるテストチップで構成されています。

インテルは、Meteor Lake Compute CPUタイルのパワーオンをすでに達成しているため、2022年2月までに最終チップを生産し、2023年に発売することが期待されます。

第14世代のMeteor Lake 7nm CPUについて、わかっていること。

インテルのMeteor Lakeシリーズのデスクトップおよびモバイル向けCPUは、新しいラインのCoveコアアーキテクチャーを採用する見込みであることなど、すでにインテルからいくつかの詳細情報を得ています。

これは「Redwood Cove」と呼ばれ、7nmのEUVプロセスノードをベースにしたものになると噂されています。

Redwood Coveは、さまざまなファブで製造可能なアグノスティック・ノードとなるように、一から設計されていると述べられています。

TSMCがRedwood Coveベースのチップのバックアップ、あるいは一部のサプライヤーであることを示唆する記述もあります。これは、IntelがCPUファミリに対して複数の製造プロセスを想定している理由を示しているのかもしれない。

Meteor LakeのCPUは、Intelがリングバスインターコネクトアーキテクチャに別れを告げる最初の世代のCPUになるかもしれません。

また、Meteor Lakeは完全な3Dスタックデザインで、外部ファブから調達したI/Oダイを利用するのではないかという噂もあります(再びTSMCの名前が挙がっています)。

インテルは、チップ上のさまざまなダイ(XPU)を相互に接続するために、Foveros Packaging TechnologyをCPUに正式に採用する予定であることが強調されています。

これは、インテルが第14世代チップの各タイルを個別に呼んでいることとも一致します(Compute Tile = CPU Cores)。

Meteor LakeデスクトップCPUファミリは、Alder LakeおよびRaptor Lakeプロセッサで使用されているのと同じLGA 1700ソケットを引き続きサポートする予定です。

また、DDR5メモリとPCIe Gen 5.0のサポートも期待できます。このプラットフォームは、DDR5とDDR4の両方のメモリをサポートします。

メインストリームおよび低価格帯の製品にはDDR4メモリDIMMが、プレミアムおよびハイエンド製品にはDDR5 DIMMが採用されます。

また、Meteor Lake PとMeteor Lake Mの両CPUは、モビリティプラットフォーム向けに開発されます。

インテルメインストリーム・デスクトップCPUの世代間比較:

| Intel CPU ファミリ | 製造 プロセス | 最大 コア数 | TDP | チップセット | プラット フォーム | メモリ サポート | PCIe サポート | 発売 |

| Sandy Bridge (2nd Gen) | 32nm | 4/8 | 35-95W | 6-Series | LGA 1155 | DDR3 | PCIe Gen 2.0 | 2011 |

| Ivy Bridge (3rd Gen) | 22nm | 4/8 | 35-77W | 7-Series | LGA 1155 | DDR3 | PCIe Gen 3.0 | 2012 |

| Haswell (4th Gen) | 22nm | 4/8 | 35-84W | 8-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2013-2014 |

| Broadwell (5th Gen) | 14nm | 4/8 | 65-65W | 9-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2015 |

| Skylake (6th Gen) | 14nm | 4/8 | 35-91W | 100-Series | LGA 1151 | DDR4/DDR3L | PCIe Gen 3.0 | 2015 |

| Kaby Lake (7th Gen) | 14nm | 4/8 | 35-91W | 200-Series | LGA 1151 | DDR4/DDR3L | PCIe Gen 3.0 | 2017 |

| Coffee Lake (8th Gen) | 14nm | 6/12 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Coffee Lake (9th Gen) | 14nm | 8/16 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2018 |

| Comet Lake (10th Gen) | 14nm | 10/20 | 35-125W | 400-Series | LGA 1200 | DDR4 | PCIe Gen 3.0 | 2020 |

| Rocket Lake (11th Gen) | 14nm | 8/16 | 35-125W | 500-Series | LGA 1200 | DDR4 | PCIe Gen 4.0 | 2021 |

| Alder Lake (12th Gen) | Intel 7 | 16/24 | 35-125W? | 600-Series | LGA 1700 | DDR5 | PCIe Gen 5.0 | 2021Q4 |

| Raptor Lake (13th Gen) | Intel 7 | 未確認 | 未確認 | 700-Series? | LGA 1700 | DDR5 | PCIe Gen 5.0 | 2022 |

| Meteor Lake (14th Gen) | Intel 4 | 未確認 | 未確認 | 800-Series? | LGA 1700 | DDR5 | PCIe Gen 5.0 | 2023 |

| Arrow Lake (15 th Gen) | Intel 4? | 40/48 | 未確認 | 900-Series? | 未確認 | DDR5 | PCIe Gen 5.0? | 2024 |

| Lunar Lake (16 th Gen) | Intel 3? | 未確認 | 未確認 | 1000-Series? | 未確認 | DDR5 | PCIe Gen 5.0? | 2025 |

| Nova Lake (17 th Gen) | Intel 3? | 未確認 | 未確認 | 2000-Series? | 未確認 | DDR5? | PCIe Gen 6.0? | 2026 |

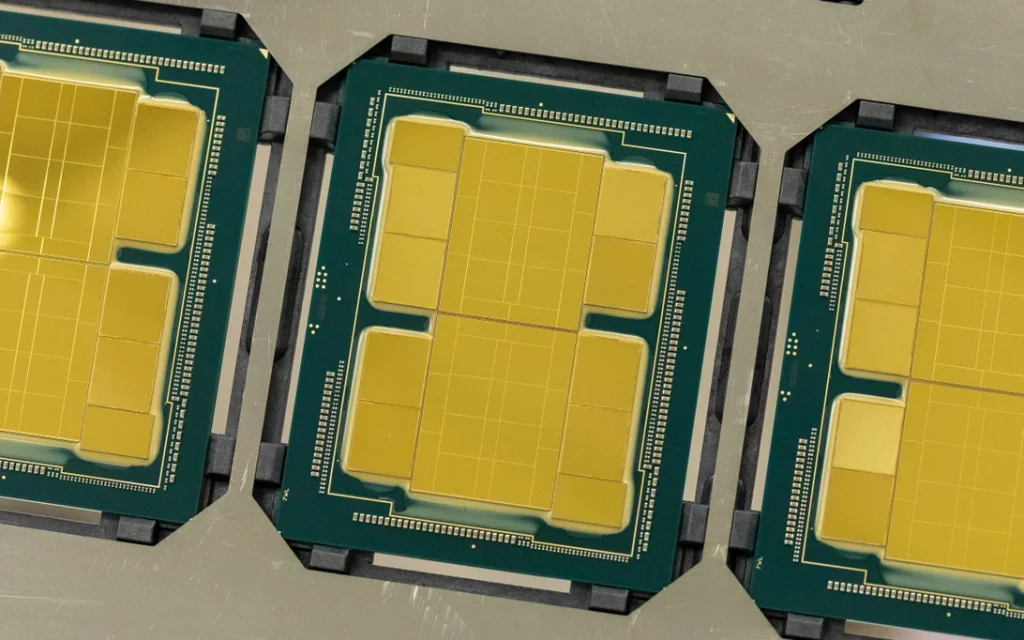

Xeonデータセンターおよびサーバー用のIntel7製造SapphireRapids CPU

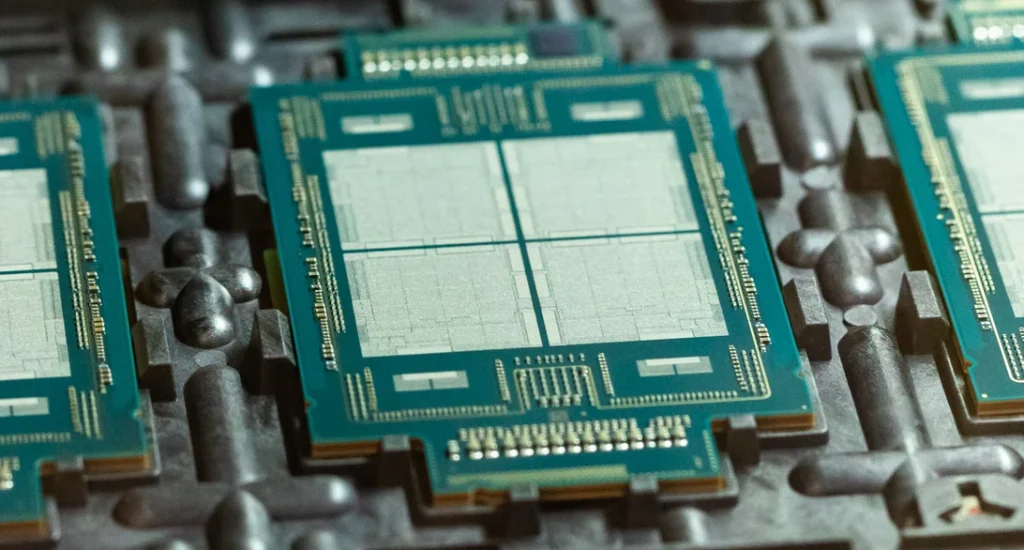

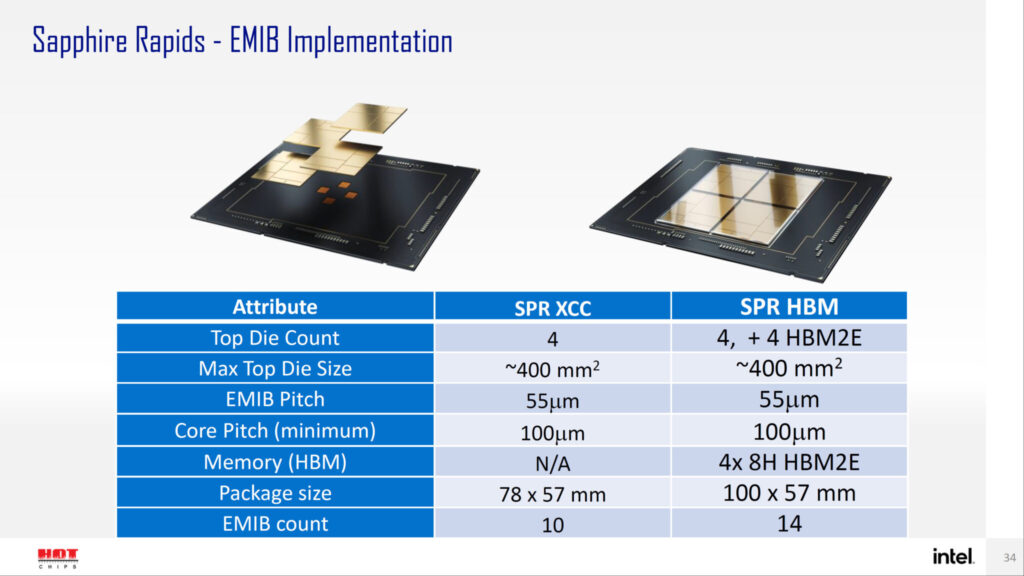

また、Intel Sapphire Rapids-SP Xeon CPUの基板、チップレット、フルパッケージデザイン(標準タイプとHBMタイプの両方)についても詳しく紹介します。

標準バージョンでは、コンピュートチップレットを搭載する4つのタイルがあります。

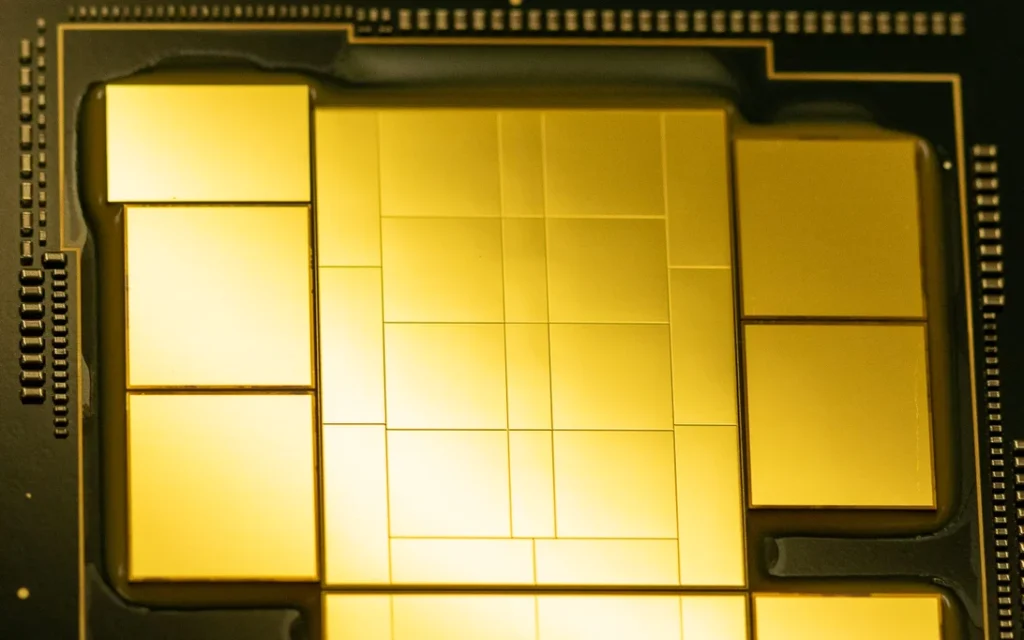

また、HBMパッケージには4つのピンアウトがあります。チップは、各ダイの端にある小さな長方形のバーであるEMIBインターコネクトを通じて、8つのチップレット(4つのコンピュート/4つのHBM)と通信します。

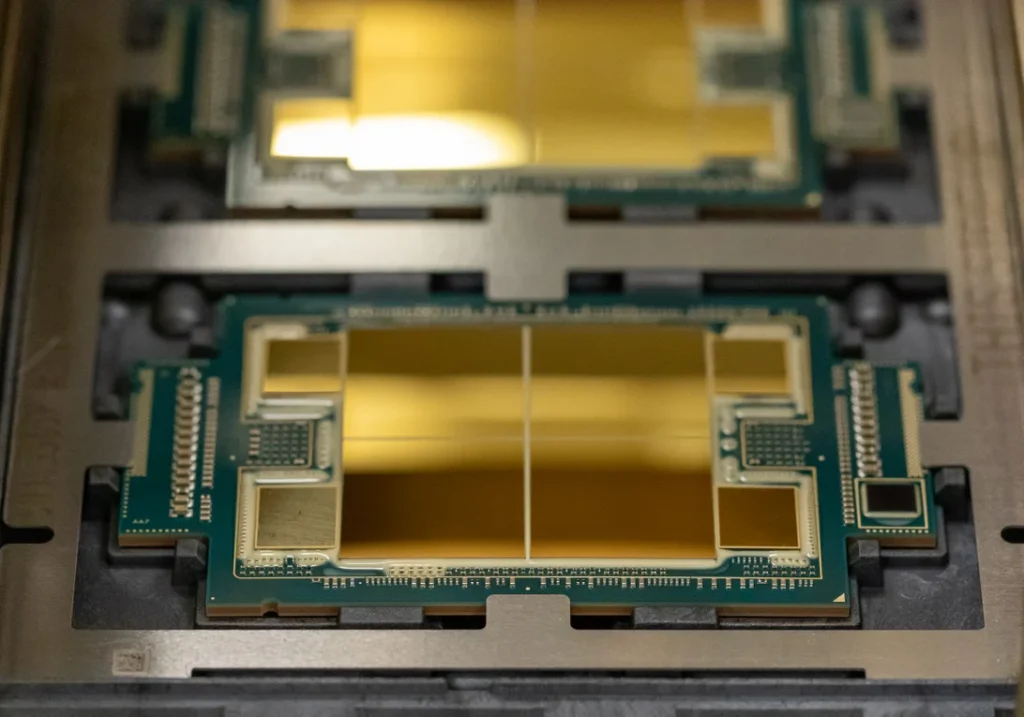

最終的な製品は以下で見ることができ、中央に4つのXeon Computeタイル、側面に4つの小さなHBM2パッケージが配置されています。

インテルは先日、Sapphire Rapids-SP Xeon CPUが最大64GBのHBM2eメモリをCPUに搭載することを確認しました。

これが今回の本格的なCPUデザインであり、2022年までに次世代データセンターへの導入が可能であることを示しています。

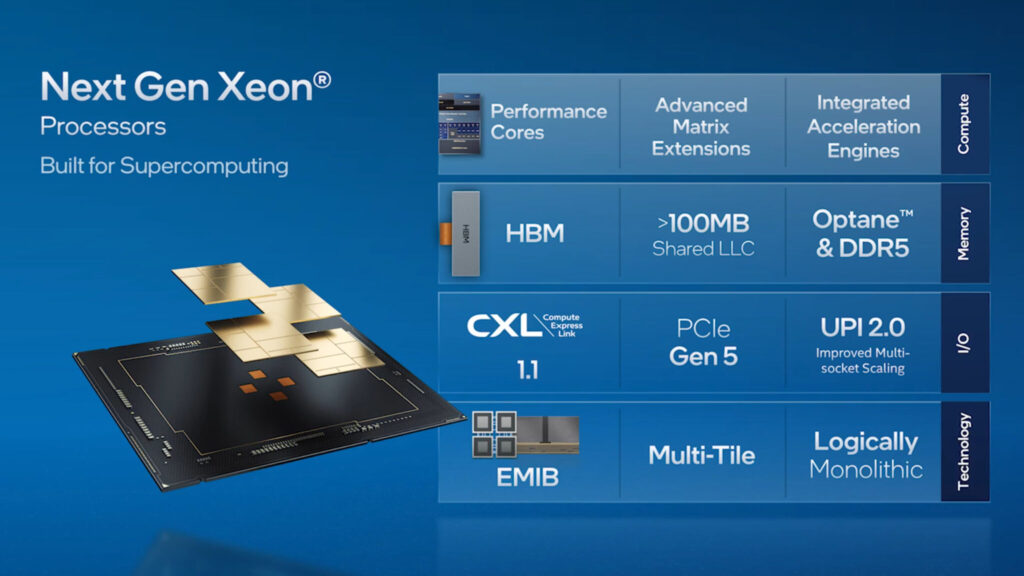

第4世代Intel Sapphire Rapids-SP Xeonファミリーについてわかっていることは以下の通りです。

Intel社によると、Sapphire Rapids-SPには、標準タイプとHBMタイプの2種類のパッケージがあります。

標準タイプは、4つのXCCダイで構成されるチップレットデザインで、ダイサイズは約400mm2です。

これはXCCダイ1個のダイサイズで、Sapphire Rapids-SP Xeonチップの最上部には合計4個のダイが搭載されます。

各ダイは、ピッチサイズ55u、コアピッチ100uのEMIBで相互に接続されます。

標準のSapphire Rapids-SP Xeonチップは、10本のEMIBインターコネクトを備えており、パッケージ全体のサイズは4446mm2と巨大です。

HBMバージョンでは、HBM2Eメモリをコアに接続するために必要な14本のインターコネクトが追加されています。

4つのHBM2Eメモリパッケージには8つのHiスタックが搭載されるため、IntelはSapphire Rapids-SPパッケージ全体で、スタックごとに少なくとも16GBのHBM2Eメモリを搭載し、合計で64GBのメモリを搭載する予定です。パッケージについて言えば、HBMタイプは5700mm2という非常に大きなサイズで、標準タイプよりも28%大きくなります。

最近リークされたEPYC Genoaの数字と比較すると、Sapphire Rapids-SPのHBM2Eパッケージは5%大きく、標準パッケージは22%小さくなります。

- Intel Sapphire Rapids-SP Xeon (Standard Package) - 4446mm2

- Intel Sapphire Rapids-SP Xeon (HBM2E Package) - 5700mm2

- AMD EPYC Genoa (12 CCD Package) - 5428mm2

また、EMIBリンクは、標準的なパッケージデザインと比較して、2倍の帯域幅密度の向上と4倍の電力効率の向上を実現しているという。

興味深いことに、Intelは最新のXeonラインナップをLogically monolithic(論理的モノリシック)と呼んでいます。

これは、シングルダイと同じ機能を提供するインターコネクトを指していますが、技術的には4つのチップレットが相互に接続されています。

標準的な56コア&112スレッドのSapphire Rapids-SP Xeon CPUに関する詳細は、こちらをご覧ください。

Intel Xeon SP ファミリ:

| ファミリー ネーム | Skylake-SP | Cascade Lake-SP/AP | Cooper Lake-SP | Ice Lake-SP | Sapphire Rapids | Emerald Rapids | Granite Rapids | Diamond Rapids |

| 製造プロセス | 14nm+ | 14nm++ | 14nm++ | 10nm+ | 10nm++ | Intel 7 | 7nm+? | Intel 3? |

| プラット フォーム | Intel Purley | Intel Purley | Intel Cedar Island | Intel Whitley | Intel Eagle Stream | Intel Eagle Stream | Intel Mountain Stream Intel Birch Stream | Intel Mountain Stream Intel Birch Stream |

| マルチ ソケット | No | Yes | No | Yes | 不明 | 不明 | 不明 | 不明 (可能性あり) |

| ソケット | LGA 3647 | LGA 3647 BGA 5903 | LGA 4189 | LGA 4189 | LGA 4677 | LGA 4677 | LGA 4677 | 不明 |

| 最大コア数 | 28 | SP28 AP 48 | 28 | 56? | 不明 | 最大64? | 不明 | 不明 |

| 最大スレッド数 | 56 | SP56 AP96 | 56 | 112? | 不明 | 最大128? | 不明 | 不明 |

| 最大L3 キャッシュ | 38.5 MB L3 | 38.5 MB L3 66 MB L3 | 38.5 MB L3 | 未確認(コア 毎に1.5 MB) | 不明 | 120 MB L3? | 不明 | 不明 |

| メモリー サポート | DDR4-2666 6-Channel | DDR4-2933 6-Channel DDR4 2933 12-Channel | 最大 6-Channel DDR4-3200 | 最大8-Channel DDR4-3200 | 8-Channel DDR5 | 最大8-Channel DDR5-5600? | 8-Channel DDR5 | 不明 |

| PCIe Gen サポート | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 4.0 (64 Lanes) | PCIe 5.0 | PCIe 5.0 | PCIe 5.0 | PCIe 6.0? |

| TDPの範囲 | 140W-205W | 165W-205W | 150W-250W | ~250W-~300W | 不明 | 最大350W | 不明 | 不明 |

| 3D Xpoint Optane DIMM | N/A | Apache Pass | Barlow Pass | Barlow Pass | Crow Pass | Crow Pass? | Donahue Pass | Donahue Pass? |

| 競合 | AMD EPYC Naples 14nm | AMD EPYC Rome 7nm | AMD EPYC Rome 7nm | AMD EPYC Milan 7nm+ | AMD EPYC Genoa ~5nm | AMD Next-Gen EPYC (Genoa後継) | AMD Next-Gen EPYC (Genoa後継) | AMD Next-Gen EPYC (Genoa後継) |

| 発売 | 2017 | 2018 | 2020 | 2020 | 2021 | 2023? | 2022-2023? | 2025 |

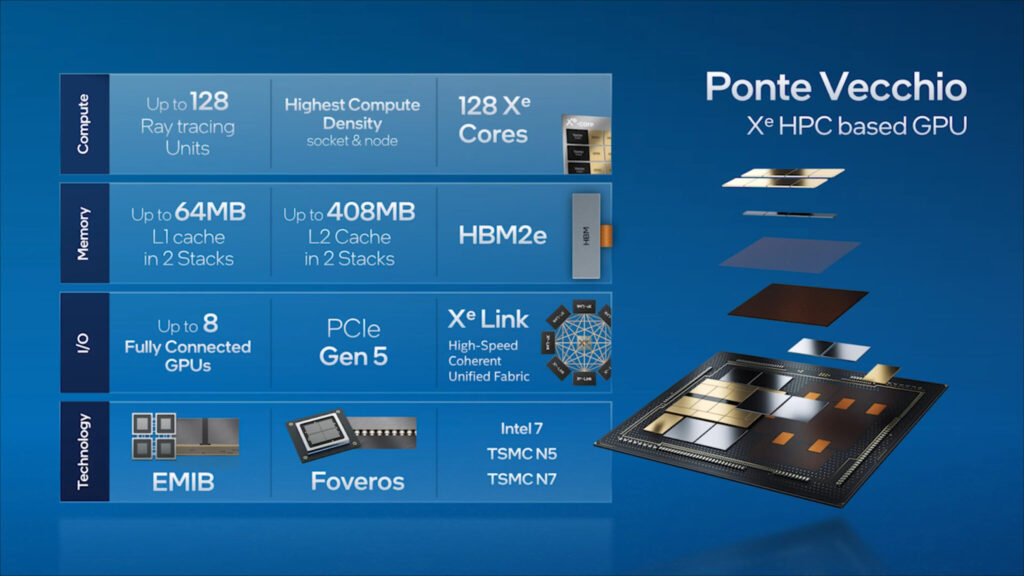

Intel7で製造されるHPC用GPU「Ponte Vecchio」が登場

最後に、次世代のHPCソリューションであるIntel Ponte Vecchio GPUの素晴らしい眺めをご紹介します。

Ponte Vecchioは、Raja Koduri氏のリーダーシップの下で設計・開発されました。

Raja Koduri氏は、このチップの設計哲学や非常に高い演算能力に関する素晴らしい情報を提供してくれました。

Intel 7を搭載したPonte Vecchio GPUについてわかっていることをまとめました。

インテルは、Ponte Vecchio GPUについて、128個のXeコア、128個のRTユニット、HBM2eメモリ、合計8個のXe-HPC GPUが接続されるなど、データセンター向けフラッグシップGPUの主な特徴を説明しました。

また、最大408MBのL2キャッシュを2つのスタックに搭載し、EMIBインターコネクトで接続します。

このチップは、インテルの「インテル7」プロセスとTSMCのN7/N5プロセスノードをベースにした複数のダイを搭載します。

また、インテルは以前、Xe-HPCアーキテクチャーをベースにしたフラッグシップGPU「Ponte Vecchio」のパッケージとダイサイズについても詳述しています。

このチップは、2つのタイルで構成され、1つのスタックに16個のアクティブダイがあります。

トップダイの最大サイズは41mm2、ベースダイのサイズは650mm2で、「Compute Tile(コンピュートタイル)」と呼ばれます。

Ponte Vecchio GPUが使用するすべてのチップレットとプロセスノードは、以下のとおりです。

- Intel 7nm

- TSMC 7nm

- Foveros 3D Packaging

- EMIB

- 10nm Enhanced Super Fin

- Rambo Cache

- HBM2

インテルがPonte Vecchioのチップに47個のタイルを搭載するまでの経緯をご紹介します:

- 16 Xe HPC (internal/external)

- 8 Rambo (internal)

- 2 Xe Base (internal)

- 11 EMIB (internal)

- 2 Xe Link (external)

- 8 HBM (external)

Ponte Vecchio GPUは、8つのHBM 8-Hiスタックを使用し、合計11本のEMIBインターコネクトを含んでいます。

インテルPonte Vecchioのパッケージ全体のサイズは4843.75mm2となる。

また、高密度3Dフォルベロスパッケージを採用したMeteor Lake CPUのバンプピッチは36uとなることも言及されている。

ポンテベッキオのGPUは、1つのチップではなく、複数のチップを組み合わせて作られています。

チップレットのパワーハウスであり、現在のGPU/CPUの中で最も多い47個のチップレットを搭載しています。

そして、これらは1つのプロセスノードではなく、数日前に説明したように複数のプロセスノードをベースにしています。

次世代データセンター用GPUアクセラレータ

| GPU名 | AMD Instinct MI200 | NVIDIA Hopper GH100 | Intel Xe HPC |

| フラッグシップ 製品 | AMD Instinct MI250X | NVIDIA H100 | Intel Ponte Vecchio |

| 半導体 パッケージ | MCM (Infinity Fabric) | MCM (NVLINK) | MCM (EMIB + Forveros) |

| GPU アーキテクチャー | Aldebaran (CDNA 2) | Hopper GH100 | Xe-HPC |

| GPU 製造プロセス | 6nm | 5nm? | 7nm (Intel 4) |

| GPUコア数 | 14080 | 18,432? | 32,768? |

| GPU クロック | 1700 MHz | 未確認 | 未確認 |

| L2 / L3 キャッシュ | 2 x 8 MB | 未確認 | 2 x 204 MB |

| FP16演算性能 | 383 TOPs | 未確認 | 未確認 |

| FP32演算性能 | 95.7 TFLOPs | 未確認 | ~45 TFLOPs (A0 Silicon) |

| FP64演算性能 | 47.9 TFLOPs | 未確認 | 未確認 |

| メモリ容量 ・種類 | 128 GB HBM2E | 128 GB HBM2E? | 未確認 |

| メモリクロック | 3.2 Gbps | 未確認 | 未確認 |

| メモリバス幅 | 8192-bit | 8192-bit? | 8192-bit |

| メモリ帯域幅 | 3.2 TB/s | ~2.5 TB/s? | 5 TB/s |

| フォームファクター | Dual Slot, Full Length / OAM | Dual Slot, Full Length / OAM | OAM |

| 冷却 | パッシブ冷却 液冷 | パッシブ冷却 液冷 | パッシブ冷却 液冷 |

| 発売時期 | 2021Q4 | 2022H2 | 2022-2023? |

インテル社のFab 42は、今後数年のうちに、次の製品を生産するFab 52およびFab 62と統合される予定です。

インテル社のCEOであるパット・ゲルシンガー氏は、9月にすでにFabの建設に着手しており、ここで次世代のサブインテル7製品が生産されることになります。

インテル・プロセス・ロードマップ

| 製造プロセス名 | Intel 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

| ステータス | 大量生産 (現在) | 生産 (現在) | 2022H2 | 2023H2 | 2024H2 | 2025H2 |

| 性能/消費電力 (対10nm ESF) | N/A | 10-15% | 20% | 18% | >20%? | 未確認 |

| EUV | N/A | N/A | 〇 | 〇 | 〇 | High-NA EUV |

| トランジスタ アーキテクチャー | FinFET | 最適化 FinFET | 最適化 FinFET | 最適化 FinFET | RibbonFET | 最適化 RibbonFET |

| 製品 | Tiger Lake | Alder Lake Sapphire Rapids Xe-HPG? | Meteor Lake Granite Rapids Xe-HPC / Xe-HP? | Lunar Lake? Diamond Rapids? 未確認 | 未確認 未確認 未確認 | 未確認 未確認 未確認 |

解説:

アリゾナ州のFab 42で撮影されたインテルの次世代CPU「Meteor Lake」、Sapphire Rapids Xeons、Ponte Vecchio GPUのダイショット写真がリークしました。

いやあ、早いですね。

RatporLakeの話が出たと思ったら、もうその次です。

MeteorLakeからはチップレットになるとのことで、4tileに分かれたチップレットが印象的です。

AMDのものと違ってかなりスマートで隙間がわずかに開いているのがわかる程度です。

ここまで形になっているとは全く思わなかったので、いずれベンチマークが出てくるかもしれませんね。

その前にRaptorLakeだと思いますが。

RaptorLakeの方はもうサンプルの配布くらいはしてるんでしょうか。

対照的に全く話が出てこなくなったのがAMDです。

一時期は破竹の勢いだったのですが、全くリークが無くなってしまいました。

一体どうなってしまったのかと心配になるほどです。

そろそろZen3+の話が出てもいいころだと思います。

Core Ultra 200Sシリーズ

ソケットLGA1851

※ 末尾にFがついているモデルはGPUがありませんのでご注意ください。