6-1.TIF

台湾半導体製造会社(TSMC)は、2nm半導体製造ノードの研究開発において、重要なブレークスルーを達成した。

台湾のメディアでは、この突破口の報道が表面化し、東部のメディアでも取り上げられている。

世界中の大小様々な企業にプロセッサなどのチップを供給しているTSMCも、2023年半ばから試作を開始し、1年後には量産を開始する見込みである。

TSMCの2nmノードは、現在のチップ製造技術の上に大きなジャンプをマークするだろう

現在、TSMCの最新の製造ノードは、2020年に向けたAppleのフラッグシップスマートフォン向けプロセッサの製造に使われる第1世代の5nmプロセスである。

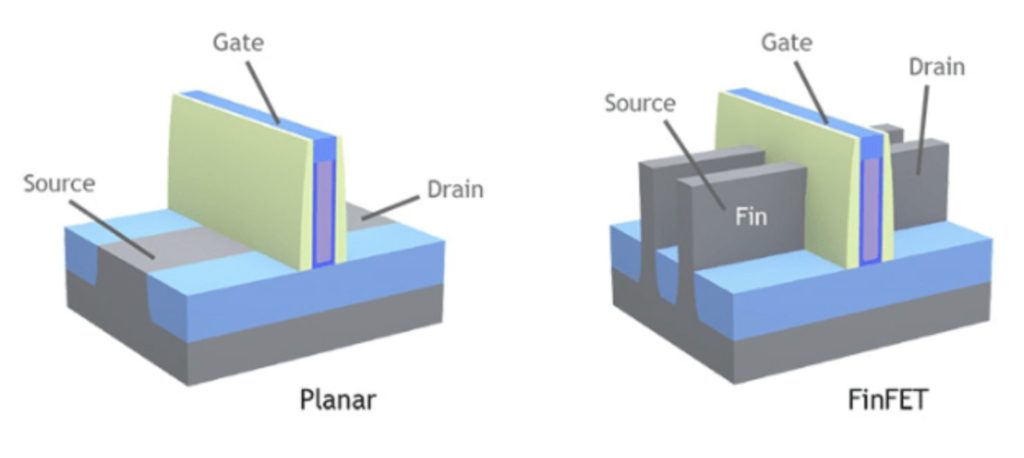

平たく言えば、「ノード」とは、トランジスタの「フィン」の寸法測定を指す。

現代のプロセッサは、このような数十億個のフィンで構成されており、これによってコンピューティングは、比類のない高度化、コスト削減、性能の向上を実現している。

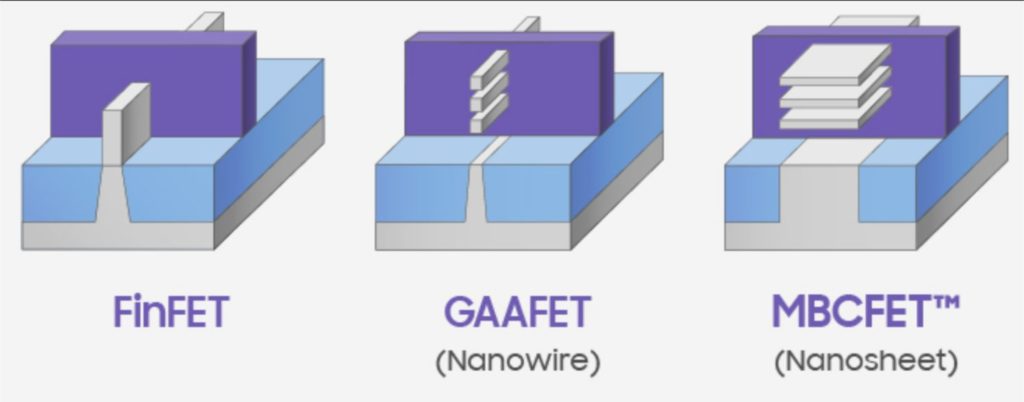

FinFET」(Fin Field Effect Transistor)とは対照的に、TSMCと韓国のChaebol Samsung ElectronicのSamsung Foundry部門が製造した製品のトランジスタの設計を説明するために使用される用語であるが、TSMCの2nmプロセスでは、差分トランジスタの設計を利用することになる。

この設計は、MBCFET(Multi-Bridge Channel Field Effect)トランジスタと呼ばれ、以前のFinFET設計に追加される。

FinFET設計には、3つの重要な要素が含まれます。

これらは、ソース、ゲート、ドレインであり、電子はソースからグレインへと流れ、ゲートはこの流れを制御します。FinFET以前の設計では、ソースとドレインは水平方向にしか製造されていませんでした。

FinFETの革新的なアプローチは、ソースとドレインの両方を3次元、つまり垂直方向に引き上げたため、ゲートを通過する電子の数が増え、リークが減り、動作電圧が低下しました。

TSMCがトランジスタにMBCFET設計を採用することを決定したのは、ファウンドリがこのような決定をするのは初めてではないだろう。

Samsungは昨年4月に3nm製造プロセス用の設計を発表しているが、同社のMBCFET設計は、2017年にIBMと共同開発して発表したGAFETトランジスタよりも進化したものだった。

SamsungのMBCFETは、同社のGAFETとは対照的に、ソースとドレイン(チャネル)にナノシートを使用しており、前者は代わりにナノワイヤを使用している。

これにより、導通に利用できる表面積が増え、さらに重要なことに、設計者は横方向の表面積を増やすことなく、トランジスタにさらに多くのゲートを追加することができます。

また、報道機関に出典のない記述が出回っているが、TSMCは、2nmプロセスノードの歩留まり率が2023年に90%という驚異的な数字に達すると予想していると示唆している。

これが実現すれば、製造プロセスが洗練され、2024年には大量生産と大量生産への移行が容易になるだろう。

Samsungは、MBCFETの発表時に、3nmトランジスタで消費電力がそれぞれ30%と45%削減され、7nm設計よりも30%性能が向上すると予想していると述べていた。

TSMCの2nmプロセスでも同様の改善が得られるかどうかは不明だが、プロセスの設計パラメータが最終的に決定された後には、より多くのことが分かるはずだ。IBMとSamsungの5nm GAAFET設計は、50mm²の表面積に300億個の驚くべきトランジスタを絞ることができた。

ソース:wccftech - TSMC To Mass Produce Breakthrough 2nm MBCFET Transistors In 2024

解説:

ついに2nmの量産時期が明らかに、2024年となる

同時にIntelにとっても最悪のお知らせです。

Intelは7nm(TSMC5nmに相当)の量産までは発表していますが、その先のTSMC3nm相当以降に関しては発表すらもされていません。

TSMC3nmは2023年となっており、すでに容量は全部予約されているとされています。

私はもっとかかると思っていたのですが、3nmの次の2nmはその次の年に量産すると言うことなので、Intelにとっては最悪の状況と言ってもよいと思います。

これだけ移行が早いと、恐らく、近いうちにIntelはTSMCに発注せざるを得ないのではないかと思います。