業界筋の噂では、半導体大手のTSMCは、技術大手のAMD、NVIDIA、MediaTek、Qualcommなどの他社による採用を増やすために、N3、すなわち3nmクラスのファブプロセスシリーズチップの価格を引き下げる可能性があるという。

この目標を達成するには、ある程度の時間とそれなりのリスクが必要ですが、TSMCのN3B技術の最大の顧客の1つであるApple以外への採用の扉を開き、より多くの機会を提供することになるでしょう。

業界関係者は、TSMCがAMDやNVIDIAのようなより多くの顧客を獲得するために、3nmプロセス技術のコスト低減を研究していることを明らかにした。

TSMCが現在直面している困難は、新しいN3技術の製造コストである。

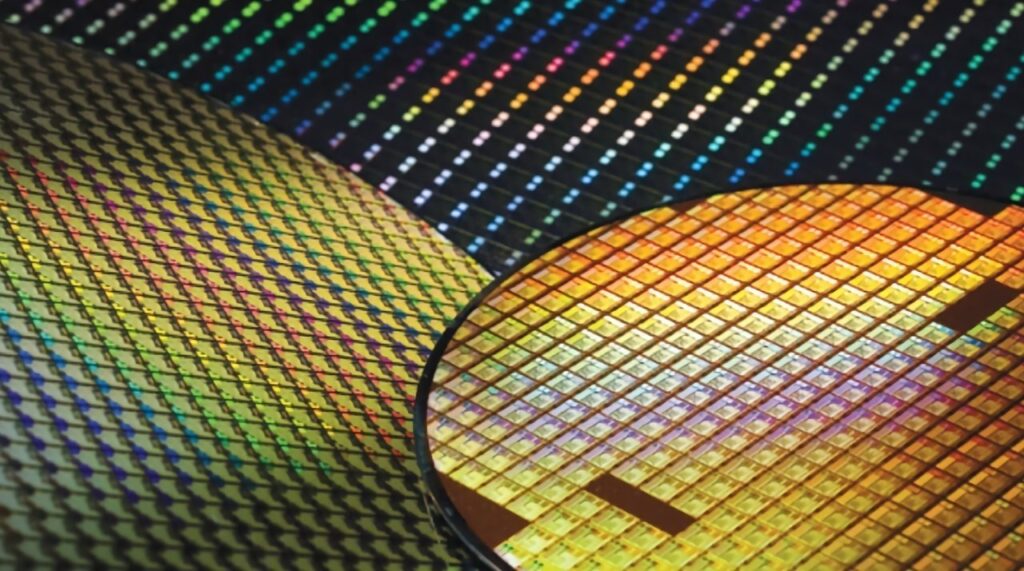

N3は25層以内のEUV(Extreme Ultraviolet)リソグラフィを利用し、EUVスキャナは構成にもよるが、1億5000万~2億ドルかかるとChina Renaissance Capital Groupは述べている。

そして、3nm技術のファウンドリ価格は、ウェハ1枚あたり2万ドルを超えるという。

AMDは以前、Zen 5マイクロアーキテクチャに3nmプロセスを活用する意向を示したが、これは早くても2024年後半まで実現しないし、NVIDIAはN3技術を将来のBlackwellベースのグラフィックスカードに採用することを目指しているという。

TSMCのCEOであるLiu Deyin氏は、3nmのファブプロセスのロジック密度は60%に高まり、消費電力レベルは同一速度で35%も低下すると報告している。

[N3]の有意義な立ち上げは、最適化版であるN3Eが完成する2023年下期だと考えている。HPC(AMD、Intelなど)、スマートフォン(QCOM、MTKなど)、ASIC(MRVL、AVGO、GUCなど)の主要顧客はN4/5にとどまり、N3EをN3クラスの初進出として選択する可能性が高いと見ている。一方、ベースラインのN3(別名N3B)の採用は、主にApple製品に限定されると考えています。

- 中国ルネッサンス・キャピタル・グループ アナリスト Szeho Ng氏

TSMCのN3プロセスノードの一つであるN3Eは、現在、わずか19層でEUVリソグラフィを利用しています。

これにより、N3P、N3S、N3Xプロセスなどの他のプロセスノードと比較して、製造が複雑でないため製造にかかるオーバーヘッドが低くなり、コストダウンにつながります。

また、製造がそれほど集中しないため、購入価格を下げるリスクも少ない。また、N5プロセスと比較してSRAMセルのスケーリングに明らかな利点はなく、チップダイのサイズアップはN3およびN3Bプロセス技術のいずれにも存在することになります。

NVIDIAは次世代GPUアーキテクチャ「Blackwell」に、AMDは次世代コアIP「Zen 5」と「RDNA 4」に3nmを活用する可能性があります。

ソース:wccftech - Insiders Inform That TSMC May Lower 3nm Costs To Swoon AMD & NVIDIA

解説:

TSMCがnVidiaとAMDのご機嫌を取るために3nmのコストを下げる研究をしている?

ライバル不在のはずのTSMC N3がコストを下げる研究をしていることが明らかになりました。

N3Eの話ならばかなり前に出ていたと思います。

こちらのことなのでしょうか。

N3Eは半導体の集積度は若干落ちますが、N3と比較すると安価にできるということでした。

元記事を見るとどうもこちらが主流になりそうな気配ですね。

それでもRTX5000シリーズはnVidia史上最も性能ジャンプする世代と言われていますので、TSMC N3世代の性能飛躍はかなり期待できるということになります。

AMDも以前公式で出していたスライドではZen5をN4で生産するということになっていましたが、元記事ではN3を検討と書かれています。

今年はZen4X3Dで、2024年はN3Eに行くという予定なのでしょうか。

この辺はハッキリしませんが、TSMCとしてはN3Eを売りたいのかもしれませんね。